Improvements in the Design and Performance of PWLL

The p-Wave Locked Loop (PWLL) provides an instantaneous measurement of the p to p time interval of the applied electrocardiogram (ECG) signal, facilitating heart rate variability studies based on p-p variations. The initial version of the PWLL began by detecting the r-wave and required manual operation of a switch to transition to p-wave detection. In subsequent versions, the transition was automated after a predetermined time. However, for patients with severe heart conditions, this fixed delay may not be sufficient, prompting the development of an improved PWLL where the transition time is dynamically adjusted based on p-p variations. This allows for rapid re-locking in cases of erratic ECG signals, with the relocking time determined by circuit components. The enhancements also include improvements in other performance characteristics, with comparisons made between the practical and ideal PWLL responses to optimize hardware parameters. This refined PWLL aids in heart rate variability studies, which are crucial for diagnosing heart diseases. The p-wave, being the first component of the ECG, offers valuable insights into the heart's pumping mechanism. However, its small amplitude and duration make it challenging to isolate from the ECG cycle. Previous attempts to separate the p-wave led to the synthesis of the PWLL, which achieved locking with the p-wave but required manual intervention. The second version automated this process after a set time, with further refinements enhancing its performance. The latest PWLL circuit captures the p-wave quickly, utilizing a sliding window approach with two monostable multivibrators and an EXOR gate. The ECG signal is amplified and thresholded to detect the r-wave, and the p-wave is amplified further for accurate measurement. The system outputs both binary and analogue forms of the p-p interval, which are used to adjust the timing window for future p-wave detections. The design incorporates adjustable threshold settings and utilizes simple edge detectors for precise timing control. The PWLL's operation is modeled as a system with specific transfer functions, allowing for stability analysis through various methods. The experimental setup includes a programmable ECG generator and a PWLL analyzer, enabling real-time data comparison and analysis of p-wave detection performance.

The p-Wave Locked Loop (PWLL) circuit is designed to enhance the detection and analysis of p-wave intervals within ECG signals, which is pivotal for heart rate variability studies and the diagnosis of cardiac conditions. The PWLL operates by first detecting the r-wave of the ECG, which serves as a reference point for the subsequent identification of the p-wave. The circuit employs a combination of analogue signal processing and digital logic to achieve this functionality.

The initial stage of the PWLL involves amplifying the incoming ECG signal to ensure that the r-wave and p-wave components are discernible. This is accomplished using a programmable gain amplifier (PGA), which adjusts the amplification based on the detected signal levels. Once the r-wave is identified through threshold comparison, the system activates a time window to anticipate the arrival of the p-wave. This window is dynamically adjusted based on the characteristics of the p-p interval, allowing for flexibility in the detection process.

To facilitate quick locking to the p-wave, the PWLL utilizes two monostable multivibrators (MSMV1 and MSMV2) that generate precise timing pulses. These pulses are used to control the timing of the detection window and ensure that the p-wave is captured efficiently. The system employs edge detection circuits, specifically positive and negative edge detectors, to accurately trigger state changes in the flip-flops that manage the counting and timing operations within the circuit.

The output of the PWLL is twofold: it provides the p-p interval in both binary and analogue formats. The binary output is generated by a counter that measures the time between successive p-waves, while the analogue output is produced by a digital-to-analogue converter (DAC). This dual output capability is crucial for various applications, including further analysis and real-time monitoring of heart rate variability.

In terms of performance, the PWLL is modeled as a system with specific transfer functions that describe its dynamic behavior. Stability analysis techniques, such as Routh-Hurwitz criteria and Nyquist stability criterion, are employed to evaluate the system's response under different conditions. Adjustments to the circuit can be made using lead and lag compensation techniques to ensure optimal performance without oscillations.

The experimental setup for testing the PWLL includes a programmable ECG generator (PEG) that simulates various ECG patterns, enabling the evaluation of the PWLL's performance across a range of scenarios. The PEG generates digitized ECG signals stored in EPROM, which are then fed into the PWLL for analysis. The output data is processed by an analyzer, allowing for real-time comparison between the actual p-wave detection and the expected performance based on the emulated data.

In conclusion, the PWLL represents a significant advancement in ECG signal processing, providing a robust tool for the analysis of heart rate variability and the diagnosis of cardiac conditions. Its design incorporates modern electronic components and methodologies to ensure accurate and efficient p-wave detection, ultimately contributing to improved patient care in cardiac health and research settings.The p-Wave Locked Loop provides instantaneously the p to p time interval of the applied ECG and enables us to perform heart rate variability studies on the basis of p_p variation. The first version of the PWLL started its processing action with the determination of r-wave first and waited for the user to operate manually a switch to transfer its a

ction for detecting p-wave and then locking to its variation. In the next version of the PWLL the changeover was made in the circuit itself after a prefixed time. Nevertheless, for certain p_p variation of severe heart patients the duration might be quite a long and the prefixed delay for changeover might fail to lock. In this improved version of the PWLL, the time duration for changing over to p_p is made dependent on p_p itself.

Therefore, the locking time is dynamic which depends on the nature of p_p variation of the ECG input. If unlocking happens due to erratic nature of the ECG it would again lock quickly and the relocking time is estimated based on circuit components and devices.

Besides the improvement in locking features, improvements in other performance characteristics of the PWLL are proposed and analyzed. A nearly ideal PWLL is emulated and the responses of the practical PWLL and emulated PWLL are compared and analyzed as to help in reaching optimum hardware parameters.

This performance improved PWLL would enable to ease further the heart rate variability studies. Cite this paper: Akin Cellatoglu, Karuppanan Balasubramanian, Improvements in the Design and Performance of PWLL, American Journal of Biomedical Engineering, Vol. 3 No. 2, 2013, pp. 41-48. doi: 10. 5923/j. ajbe. 20130302. 02. Heart rate variability studies performed in cardiac health and research centres have been helpful in analysing the heart diseases of the patients so as to diagnose the seriousness of illness needed for taking appropriate treatment.

The heart rate variability studies made on the consistency of p-wave interval in ECG has given more promising results in the diagnosis of heart diseases. As the p-wave occurs first in the ECG, the pumping mechanism of heart is better revealed by the p-wave[1, 2].

Since the p-wave is relatively a small part in time and in amplitude in the cardiac waveform it is more difficult to separate it from the rest of the ECG cycle. In the past an electronic device to separate the p-wave from the rest of waves of ECG was reported[3].

As it was not locking with the applied ECG for p wave a PWLL (p-wave Locked Loop) was synthesized and reported[4-6]. The first PWLL reported locked itself with the p-wave of the ECG but needed a manual changeover operation for locking to take place.

The second versions of the PWLL[7] has made the change over for p-wave for automatic locking after a set predetermined time. Further minor modifications were made in that version [8] for improving its characteristics a bit further.

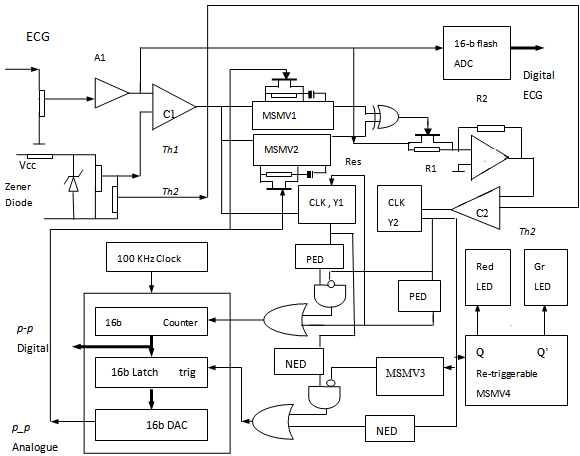

Now we make additional improvements in the PWLL circuit which performs quick catching of locking from unlocking instants necessitated by erratic behaviour of p-to-p variation in the ECG. Therefore, the PWLL gets locked to the p-wave as quickly as possible. Moreover, the design parameters of the PWLL are set according to system theory. The block schematic of the p-Wave Locked Loop incorporating the improved design features is shown in Figure 1.

The PWLL needs analogue ECG input for generating the locking conditions of p-wave that provides the p_p interval in both analogue and digital form. From the analogue ECG signal input the r-wave is detected in PWLL by threshold comparison and the proximity of the occurrence of the next p-wave is time slotted as a window.

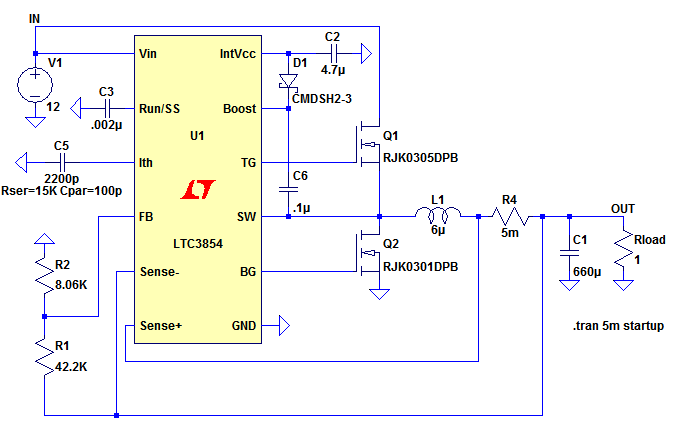

In this process, the time window predicting the expected time location of p-wave is fixed and the p-wave arising as a part of the ECG in this window is amplified to a greater extent. The PWLL gets locked to p-wave shortly and provides p_p time in binary and analogue form. The circuit of PWLL with improved design is shown in Figure 2. The design parameters are set according to the system theory and the changeover time from r_r to p_p locking is made automatic ensuring of a minimal time lapse.

Catching the p-wave and locking to it takes a bit time in accordance with the nature of variations of p_p. The sliding window for p-wave detection is set with two monostable multivibrators (MSMV1 and MSMV2) and EXOR gate.

The ECG is amplified (A1) and compared (C1) with a threshold as to detect r-wave for triggering the monostable multivibrators. The pulsing periods of the monostables are controlled by the resistance and capacitance extended to them.

Each resistance is programmable with the use of FET extended to it. The gate drive changes its RdsON and the resistance extended to monostables. Therefore, each FET works as a voltage controlled resistor. The programmable gain amplifier (PGA) amplifies (A2) the low amplitude p-wave to a larger value like r-wave as the gain set during this time slot with the concerned FET would be high. The amplified p-wave is then threshold detected and processed in a binary counter as to determine time interval between successive p-waves and presented as binary p_p output.

This binary p_p is converted into analogue form with a DAC (Digital to Analogue Converter) and this is also presented as another output. This analogue p_p is used to adjust the next p-wave time slot window as to place it in the expected time position of the incoming p-wave.

The time slot therefore adjusts automatically with the present value of p_p. Depending upon the circuit conditions the threshold setting is adjustable with external input. Precision setting of the threshold voltages Th1 and Th2 are performed with a Zener diode and potentiometers shown. The r-wave clocks a flip flop Y2 and the p-wave clocks the flip flop Y1. Initially Y2 controls the reset input of the counter and trigger input of the latch. After catching the p-wave Y1 takes charge of these activities. Simple edge detectors using NAND gates[9] performing as the Positive Edge Detector (PED) and Negative Edge Detector (NED) circuits are used in the PWLL.

The monostable MSMV3 extends Y2 period to such an extent as to avoid the retriggering of the latch by Y2. As the p-wave occurs first in the ECG, once it is caught it resets Y2 as to begin its waveform. Figure 3 shows the timing diagram illustrating various activities in PWLL. In this example, after the lapse of two r-waves the p-wave is caught. If in case p-wave location identification takes a few cycles of ECG, monitoring of r-wave will be continuing until the catching instant of p-wave.

In these transition circumstances the counter would produce the r_r count. The p_p locking is indicated by a RED LED and working with r_r is denoted by green LED. Its drive is materialized with a re-triggerable monostable MSMV4 shown in Figure 2. The analogue ECG input given to PWLL is digitized with a 16-b flash ADC (Analogue to Digital Converter) built under advanced architecture[10] and the binary form of the ECG is also made available for further processing and display operations that may be required. The conventional PLL[11] works entirely in a different approach. It has a definite frequency range for locking to take place with the applied signal. Unlike PLL, the input to PWLL is always the ECG and it ensures locking with p-wave for any shape of ECG.

Nevertheless, the locking time with p-wave differs from one pattern of ECG than the other. Locating the p-window and boosting the p-wave is performed with monostables, FETs and PGA. If the ON resistance of the drain to source, (RdsON) of the FET connected across the resistor R1 of the PGA is rp then the gain at the instant of window time would be Based on the actions performed in the PWLL it is modeled as a system and its block diagram is shown in Figure 4. The window slotting and obtaining the p window is modeled as K2/(s+a). The parameters K2 and a depend on the device parameter RdsON of the FET and the circuit components such as the resistors and the capacitors used.

Getting p_p count from the p-window is modeled as an integrator (1/s). The p_p is made available in both binary and analogue form. With a potentiometer action the analogue p_p acts as error signal ”rp to the FET extended to the MSMV. This in turn slips from r-wave detected into p-wave slotting action termed as r_p. Accordingly, the transfer function of the PWLL is evolved as follows. The PWLL circuit with the above transfer function with second order characteristic equation can be analyzed as to assess its static and dynamic performances.

As in conventional approaches, Bode plots and polar plots can be made as to provide the basis for further analysis. In time domain analysis Routh-Hurwitz and Root-locus methods are applied[12] as to determine the stability.

Another popular approach is Nyquist stability criterion that determines the stability of the closed loop transfer function Gf (jw) from the open loop transfer function G (jw). In order to ensure stability, if required, lead compensation and lag compensation techniques could be applied by appropriate use of op-amp with capacitors and resistors incorporated at the selected parts of the circuit introducing additional poles or zeros.

In an attempt to avoid oscillations in PWLL we set the damping factor ¶ to be kept at unity. The practical PWLL needs first the range of r_r and p_p encountered in practice as to decide the p-window delay. They are decided based on the statistical information available in practice with ECGs of various kinds of heart diseases.

Accordingly the FETs used for controlling the time factors through their resistors and capacitors are designed and fixed. This would set the values of the constants K2 and a controlling the transfer from r_r to p_p. The main electronic devices and circuits used in PWLL are programmable gain amplifier, monostable multivibrators, binary counter, ADC, DAC, logic gates, flip flops and analogue comparators.

The loop gain and locking range are affected by the characteristics and operating ranges of these electronic devices. The PWLL is synthesized based on the requirements satisfying the system theory and put into use. In order to assess the performance of the PWLL we need to provide the ECG input of varied nature and standards collected from different clauses of heart patients.

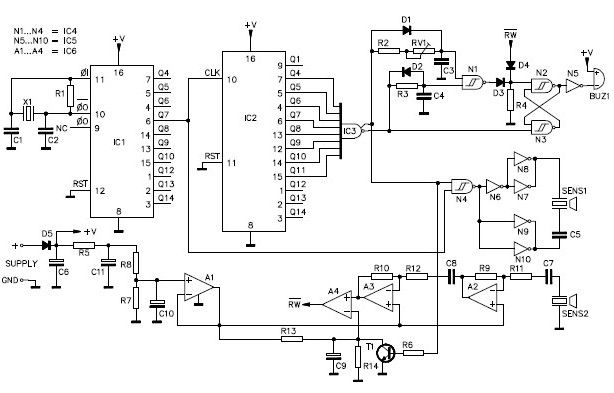

They have p_p intervals changing progressively and also abruptly. Also the magnitudes and shape of p-wave might have variations. The practical ECG recorded from a standard ECG instrument is saved and loaded in the EPROM of the test setup for experimentation. The experimental setup which provides these features for experimentation is shown in Figure 5. It has two parts. The first part is programmable ECG generator (PEG) and the second part is PWLL analyzer. The ECG obtained from PEG is applied to the PWLL. The analyzer is a computer (laptop or PC) where the PWLL emulator package is loaded. The analyzer receives the p_p data from the PEG and also from the emulator. The emulator is producing optimal p_p data describing about the catching of p-wave and locking nature and its variations.

The analyzer package performs the comparison of these two data in real time and produces the message accordingly. The main output of analyzer would be the differences in catching time of p-wave from reset conditions, unlocking instants, if any, p_p variations, variances of p_p and standard deviations in p_p.

The emulator package is developed on the circuit maker[13] platform which could receive the external ECG in real time mode. Most devices and components used are commonly available in practice. The output from the emulator is captured and saved in a block of memory on FIFO basis. The PEG works on lookup table approach. Digitized samples of various patterns of ECGs are stored in EPROM in page wise. Each pattern of ECG has 4K samples covering 10 complete cycles of it. With twin 64K EPROMs, 16 ECG patterns are loaded and used. The EPROM therefore has 16-b address and 16-b data. A pattern available in a page is selected externally by setting four most significant address bits of the EPROM.

A 12-b binary counter extended to least significant 12 bits of EPROM accesses sequentially the locations of the selected page. This arrangement would read the 4K samples successively to DAC as to get analogue ECG waveform from the DAC.

While running it repeats the action cyclically and produces analogue ECG continuously. This is further added with random noise generator of chosen amplitude as to get the noise infected ECG and this is driven to the PWLL. The voltage level of the noise is kept slightly lower than the magnitude of standard p-wave. This noise induction is needed to account for any error in shape or jitter in waveform generated by the ECG instruments used in practice.

🔗 External reference

The p-Wave Locked Loop (PWLL) circuit is designed to enhance the detection and analysis of p-wave intervals within ECG signals, which is pivotal for heart rate variability studies and the diagnosis of cardiac conditions. The PWLL operates by first detecting the r-wave of the ECG, which serves as a reference point for the subsequent identification of the p-wave. The circuit employs a combination of analogue signal processing and digital logic to achieve this functionality.

The initial stage of the PWLL involves amplifying the incoming ECG signal to ensure that the r-wave and p-wave components are discernible. This is accomplished using a programmable gain amplifier (PGA), which adjusts the amplification based on the detected signal levels. Once the r-wave is identified through threshold comparison, the system activates a time window to anticipate the arrival of the p-wave. This window is dynamically adjusted based on the characteristics of the p-p interval, allowing for flexibility in the detection process.

To facilitate quick locking to the p-wave, the PWLL utilizes two monostable multivibrators (MSMV1 and MSMV2) that generate precise timing pulses. These pulses are used to control the timing of the detection window and ensure that the p-wave is captured efficiently. The system employs edge detection circuits, specifically positive and negative edge detectors, to accurately trigger state changes in the flip-flops that manage the counting and timing operations within the circuit.

The output of the PWLL is twofold: it provides the p-p interval in both binary and analogue formats. The binary output is generated by a counter that measures the time between successive p-waves, while the analogue output is produced by a digital-to-analogue converter (DAC). This dual output capability is crucial for various applications, including further analysis and real-time monitoring of heart rate variability.

In terms of performance, the PWLL is modeled as a system with specific transfer functions that describe its dynamic behavior. Stability analysis techniques, such as Routh-Hurwitz criteria and Nyquist stability criterion, are employed to evaluate the system's response under different conditions. Adjustments to the circuit can be made using lead and lag compensation techniques to ensure optimal performance without oscillations.

The experimental setup for testing the PWLL includes a programmable ECG generator (PEG) that simulates various ECG patterns, enabling the evaluation of the PWLL's performance across a range of scenarios. The PEG generates digitized ECG signals stored in EPROM, which are then fed into the PWLL for analysis. The output data is processed by an analyzer, allowing for real-time comparison between the actual p-wave detection and the expected performance based on the emulated data.

In conclusion, the PWLL represents a significant advancement in ECG signal processing, providing a robust tool for the analysis of heart rate variability and the diagnosis of cardiac conditions. Its design incorporates modern electronic components and methodologies to ensure accurate and efficient p-wave detection, ultimately contributing to improved patient care in cardiac health and research settings.The p-Wave Locked Loop provides instantaneously the p to p time interval of the applied ECG and enables us to perform heart rate variability studies on the basis of p_p variation. The first version of the PWLL started its processing action with the determination of r-wave first and waited for the user to operate manually a switch to transfer its a

ction for detecting p-wave and then locking to its variation. In the next version of the PWLL the changeover was made in the circuit itself after a prefixed time. Nevertheless, for certain p_p variation of severe heart patients the duration might be quite a long and the prefixed delay for changeover might fail to lock. In this improved version of the PWLL, the time duration for changing over to p_p is made dependent on p_p itself.

Therefore, the locking time is dynamic which depends on the nature of p_p variation of the ECG input. If unlocking happens due to erratic nature of the ECG it would again lock quickly and the relocking time is estimated based on circuit components and devices.

Besides the improvement in locking features, improvements in other performance characteristics of the PWLL are proposed and analyzed. A nearly ideal PWLL is emulated and the responses of the practical PWLL and emulated PWLL are compared and analyzed as to help in reaching optimum hardware parameters.

This performance improved PWLL would enable to ease further the heart rate variability studies. Cite this paper: Akin Cellatoglu, Karuppanan Balasubramanian, Improvements in the Design and Performance of PWLL, American Journal of Biomedical Engineering, Vol. 3 No. 2, 2013, pp. 41-48. doi: 10. 5923/j. ajbe. 20130302. 02. Heart rate variability studies performed in cardiac health and research centres have been helpful in analysing the heart diseases of the patients so as to diagnose the seriousness of illness needed for taking appropriate treatment.

The heart rate variability studies made on the consistency of p-wave interval in ECG has given more promising results in the diagnosis of heart diseases. As the p-wave occurs first in the ECG, the pumping mechanism of heart is better revealed by the p-wave[1, 2].

Since the p-wave is relatively a small part in time and in amplitude in the cardiac waveform it is more difficult to separate it from the rest of the ECG cycle. In the past an electronic device to separate the p-wave from the rest of waves of ECG was reported[3].

As it was not locking with the applied ECG for p wave a PWLL (p-wave Locked Loop) was synthesized and reported[4-6]. The first PWLL reported locked itself with the p-wave of the ECG but needed a manual changeover operation for locking to take place.

The second versions of the PWLL[7] has made the change over for p-wave for automatic locking after a set predetermined time. Further minor modifications were made in that version [8] for improving its characteristics a bit further.

Now we make additional improvements in the PWLL circuit which performs quick catching of locking from unlocking instants necessitated by erratic behaviour of p-to-p variation in the ECG. Therefore, the PWLL gets locked to the p-wave as quickly as possible. Moreover, the design parameters of the PWLL are set according to system theory. The block schematic of the p-Wave Locked Loop incorporating the improved design features is shown in Figure 1.

The PWLL needs analogue ECG input for generating the locking conditions of p-wave that provides the p_p interval in both analogue and digital form. From the analogue ECG signal input the r-wave is detected in PWLL by threshold comparison and the proximity of the occurrence of the next p-wave is time slotted as a window.

In this process, the time window predicting the expected time location of p-wave is fixed and the p-wave arising as a part of the ECG in this window is amplified to a greater extent. The PWLL gets locked to p-wave shortly and provides p_p time in binary and analogue form. The circuit of PWLL with improved design is shown in Figure 2. The design parameters are set according to the system theory and the changeover time from r_r to p_p locking is made automatic ensuring of a minimal time lapse.

Catching the p-wave and locking to it takes a bit time in accordance with the nature of variations of p_p. The sliding window for p-wave detection is set with two monostable multivibrators (MSMV1 and MSMV2) and EXOR gate.

The ECG is amplified (A1) and compared (C1) with a threshold as to detect r-wave for triggering the monostable multivibrators. The pulsing periods of the monostables are controlled by the resistance and capacitance extended to them.

Each resistance is programmable with the use of FET extended to it. The gate drive changes its RdsON and the resistance extended to monostables. Therefore, each FET works as a voltage controlled resistor. The programmable gain amplifier (PGA) amplifies (A2) the low amplitude p-wave to a larger value like r-wave as the gain set during this time slot with the concerned FET would be high. The amplified p-wave is then threshold detected and processed in a binary counter as to determine time interval between successive p-waves and presented as binary p_p output.

This binary p_p is converted into analogue form with a DAC (Digital to Analogue Converter) and this is also presented as another output. This analogue p_p is used to adjust the next p-wave time slot window as to place it in the expected time position of the incoming p-wave.

The time slot therefore adjusts automatically with the present value of p_p. Depending upon the circuit conditions the threshold setting is adjustable with external input. Precision setting of the threshold voltages Th1 and Th2 are performed with a Zener diode and potentiometers shown. The r-wave clocks a flip flop Y2 and the p-wave clocks the flip flop Y1. Initially Y2 controls the reset input of the counter and trigger input of the latch. After catching the p-wave Y1 takes charge of these activities. Simple edge detectors using NAND gates[9] performing as the Positive Edge Detector (PED) and Negative Edge Detector (NED) circuits are used in the PWLL.

The monostable MSMV3 extends Y2 period to such an extent as to avoid the retriggering of the latch by Y2. As the p-wave occurs first in the ECG, once it is caught it resets Y2 as to begin its waveform. Figure 3 shows the timing diagram illustrating various activities in PWLL. In this example, after the lapse of two r-waves the p-wave is caught. If in case p-wave location identification takes a few cycles of ECG, monitoring of r-wave will be continuing until the catching instant of p-wave.

In these transition circumstances the counter would produce the r_r count. The p_p locking is indicated by a RED LED and working with r_r is denoted by green LED. Its drive is materialized with a re-triggerable monostable MSMV4 shown in Figure 2. The analogue ECG input given to PWLL is digitized with a 16-b flash ADC (Analogue to Digital Converter) built under advanced architecture[10] and the binary form of the ECG is also made available for further processing and display operations that may be required. The conventional PLL[11] works entirely in a different approach. It has a definite frequency range for locking to take place with the applied signal. Unlike PLL, the input to PWLL is always the ECG and it ensures locking with p-wave for any shape of ECG.

Nevertheless, the locking time with p-wave differs from one pattern of ECG than the other. Locating the p-window and boosting the p-wave is performed with monostables, FETs and PGA. If the ON resistance of the drain to source, (RdsON) of the FET connected across the resistor R1 of the PGA is rp then the gain at the instant of window time would be Based on the actions performed in the PWLL it is modeled as a system and its block diagram is shown in Figure 4. The window slotting and obtaining the p window is modeled as K2/(s+a). The parameters K2 and a depend on the device parameter RdsON of the FET and the circuit components such as the resistors and the capacitors used.

Getting p_p count from the p-window is modeled as an integrator (1/s). The p_p is made available in both binary and analogue form. With a potentiometer action the analogue p_p acts as error signal ”rp to the FET extended to the MSMV. This in turn slips from r-wave detected into p-wave slotting action termed as r_p. Accordingly, the transfer function of the PWLL is evolved as follows. The PWLL circuit with the above transfer function with second order characteristic equation can be analyzed as to assess its static and dynamic performances.

As in conventional approaches, Bode plots and polar plots can be made as to provide the basis for further analysis. In time domain analysis Routh-Hurwitz and Root-locus methods are applied[12] as to determine the stability.

Another popular approach is Nyquist stability criterion that determines the stability of the closed loop transfer function Gf (jw) from the open loop transfer function G (jw). In order to ensure stability, if required, lead compensation and lag compensation techniques could be applied by appropriate use of op-amp with capacitors and resistors incorporated at the selected parts of the circuit introducing additional poles or zeros.

In an attempt to avoid oscillations in PWLL we set the damping factor ¶ to be kept at unity. The practical PWLL needs first the range of r_r and p_p encountered in practice as to decide the p-window delay. They are decided based on the statistical information available in practice with ECGs of various kinds of heart diseases.

Accordingly the FETs used for controlling the time factors through their resistors and capacitors are designed and fixed. This would set the values of the constants K2 and a controlling the transfer from r_r to p_p. The main electronic devices and circuits used in PWLL are programmable gain amplifier, monostable multivibrators, binary counter, ADC, DAC, logic gates, flip flops and analogue comparators.

The loop gain and locking range are affected by the characteristics and operating ranges of these electronic devices. The PWLL is synthesized based on the requirements satisfying the system theory and put into use. In order to assess the performance of the PWLL we need to provide the ECG input of varied nature and standards collected from different clauses of heart patients.

They have p_p intervals changing progressively and also abruptly. Also the magnitudes and shape of p-wave might have variations. The practical ECG recorded from a standard ECG instrument is saved and loaded in the EPROM of the test setup for experimentation. The experimental setup which provides these features for experimentation is shown in Figure 5. It has two parts. The first part is programmable ECG generator (PEG) and the second part is PWLL analyzer. The ECG obtained from PEG is applied to the PWLL. The analyzer is a computer (laptop or PC) where the PWLL emulator package is loaded. The analyzer receives the p_p data from the PEG and also from the emulator. The emulator is producing optimal p_p data describing about the catching of p-wave and locking nature and its variations.

The analyzer package performs the comparison of these two data in real time and produces the message accordingly. The main output of analyzer would be the differences in catching time of p-wave from reset conditions, unlocking instants, if any, p_p variations, variances of p_p and standard deviations in p_p.

The emulator package is developed on the circuit maker[13] platform which could receive the external ECG in real time mode. Most devices and components used are commonly available in practice. The output from the emulator is captured and saved in a block of memory on FIFO basis. The PEG works on lookup table approach. Digitized samples of various patterns of ECGs are stored in EPROM in page wise. Each pattern of ECG has 4K samples covering 10 complete cycles of it. With twin 64K EPROMs, 16 ECG patterns are loaded and used. The EPROM therefore has 16-b address and 16-b data. A pattern available in a page is selected externally by setting four most significant address bits of the EPROM.

A 12-b binary counter extended to least significant 12 bits of EPROM accesses sequentially the locations of the selected page. This arrangement would read the 4K samples successively to DAC as to get analogue ECG waveform from the DAC.

While running it repeats the action cyclically and produces analogue ECG continuously. This is further added with random noise generator of chosen amplitude as to get the noise infected ECG and this is driven to the PWLL. The voltage level of the noise is kept slightly lower than the magnitude of standard p-wave. This noise induction is needed to account for any error in shape or jitter in waveform generated by the ECG instruments used in practice.

🔗 External reference