Input Impedance Booster II

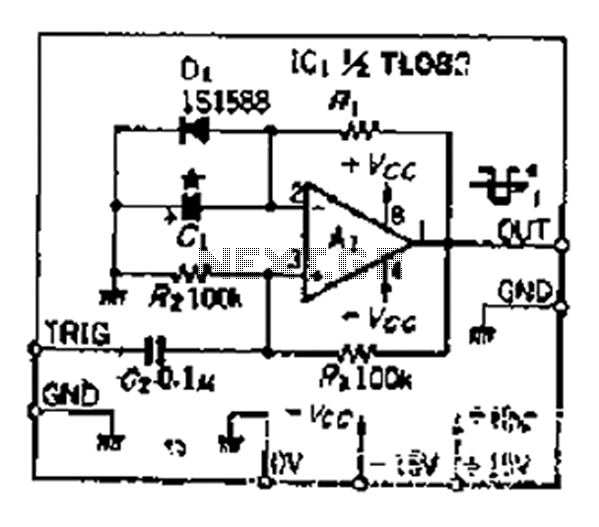

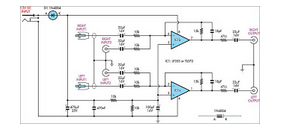

The input resistance of AC-coupled operational amplifier circuits is primarily determined by the resistance used for DC biasing. When using CMOS operational amplifiers, the input resistance is typically high, reaching up to 10 MΩ. For applications requiring even higher input resistance, a bootstrap circuit can be implemented to artificially increase the input resistance to very high levels. In the provided circuit diagram, resistor R1 establishes the DC operating point for IC1a. The terminal of R1 connected to pin 7 of IC1 is usually at ground potential, resulting in an input impedance of 10 MΩ. By connecting the other terminal of R1 to ground through IC1a and the network formed by capacitors C2 and resistors R3 and R2, the necessary DC biasing for the operational amplifier is achieved. For AC signals, feedback is applied so that only a minimal alternating current flows through R1. Consequently, the input resistance, Rin, can be expressed as Rin = R1[(R2 + R3)/R3]. With the specified resistor values, Rin is approximately 1 GΩ. It is crucial to note that the ratio (R2 + R3)/R3 must not exceed 0.99, which implies that R3 should not be less than 100 kΩ if R2 is set to 10 MΩ. Failure to adhere to these conditions may lead to circuit instability.

In the context of this AC-coupled operational amplifier circuit, the input resistance plays a critical role in determining the overall performance and stability of the system. The use of CMOS technology is beneficial due to its high input impedance, which minimizes loading effects on the preceding stage. The bootstrap technique is particularly useful for applications requiring extremely high input resistance, as it allows for the effective enhancement of the impedance seen at the input without introducing significant noise or distortion.

The configuration of resistor R1 is pivotal in establishing the desired DC operating point, ensuring that the operational amplifier functions within its optimal range. The feedback network, comprising capacitors and resistors, is designed to facilitate proper AC signal handling while maintaining the DC biasing conditions. The careful selection of resistor values is essential for achieving the target input resistance; hence, adherence to the specified limits on R3 and R2 is critical to prevent instability.

In practical applications, such circuits can be utilized in various signal processing tasks, including sensor interfacing, audio processing, and instrumentation, where high input resistance is paramount. The design considerations outlined ensure that the circuit remains stable and performs effectively across a range of operating conditions.The input resistance of a. c. -coupled op amp circuits depends almost entirely on the resistance with which the d. c. setting is determined. If CMOS op amps are used, the input resistance is normally high, currently up to 10 M. If a higher value is needed, a bootstrap circuit may be used. This enables the input resistance to be boosted artificiall y to a very high value, indeed In the circuit shown in the diagram, resistor R1 sets the d. c. point for IC1a. The terminal of the resistor linked to pin 7 of IC1 would normally be at earth potential, so that the input impedance would be 10 M. Connecting the other terminal of the resistor to earth via IC1a and network C2-R3-R2 as far as d. c. is concerned results in the requisite d. c. setting of the op amp. As far as alternating voltages are concerned, the input signal is fed back so that only a tiny alternating current flows through R1.

Therefore, Rin=R1[(R2+R3)/R3]. With resistor values as specified, Rin is about 1 G. One aspect must be borne in mind: the numerical value of (R2+R3)/R3 must not exceed 0. 99. This means that the value of R3 cannot be less than 100 k if the value of R2 is 10 M. If these conditions are not met, the circuit will become unstable. 🔗 External reference

In the context of this AC-coupled operational amplifier circuit, the input resistance plays a critical role in determining the overall performance and stability of the system. The use of CMOS technology is beneficial due to its high input impedance, which minimizes loading effects on the preceding stage. The bootstrap technique is particularly useful for applications requiring extremely high input resistance, as it allows for the effective enhancement of the impedance seen at the input without introducing significant noise or distortion.

The configuration of resistor R1 is pivotal in establishing the desired DC operating point, ensuring that the operational amplifier functions within its optimal range. The feedback network, comprising capacitors and resistors, is designed to facilitate proper AC signal handling while maintaining the DC biasing conditions. The careful selection of resistor values is essential for achieving the target input resistance; hence, adherence to the specified limits on R3 and R2 is critical to prevent instability.

In practical applications, such circuits can be utilized in various signal processing tasks, including sensor interfacing, audio processing, and instrumentation, where high input resistance is paramount. The design considerations outlined ensure that the circuit remains stable and performs effectively across a range of operating conditions.The input resistance of a. c. -coupled op amp circuits depends almost entirely on the resistance with which the d. c. setting is determined. If CMOS op amps are used, the input resistance is normally high, currently up to 10 M. If a higher value is needed, a bootstrap circuit may be used. This enables the input resistance to be boosted artificiall y to a very high value, indeed In the circuit shown in the diagram, resistor R1 sets the d. c. point for IC1a. The terminal of the resistor linked to pin 7 of IC1 would normally be at earth potential, so that the input impedance would be 10 M. Connecting the other terminal of the resistor to earth via IC1a and network C2-R3-R2 as far as d. c. is concerned results in the requisite d. c. setting of the op amp. As far as alternating voltages are concerned, the input signal is fed back so that only a tiny alternating current flows through R1.

Therefore, Rin=R1[(R2+R3)/R3]. With resistor values as specified, Rin is about 1 G. One aspect must be borne in mind: the numerical value of (R2+R3)/R3 must not exceed 0. 99. This means that the value of R3 cannot be less than 100 k if the value of R2 is 10 M. If these conditions are not met, the circuit will become unstable. 🔗 External reference