Low-Cost Window Comparator

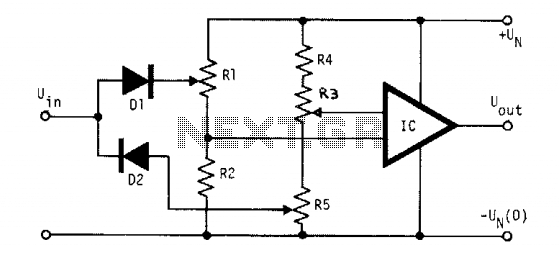

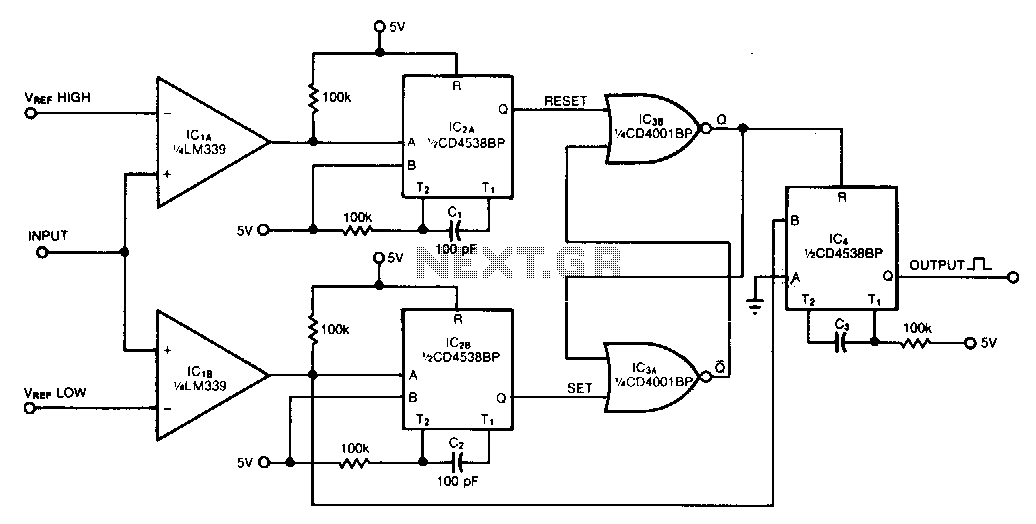

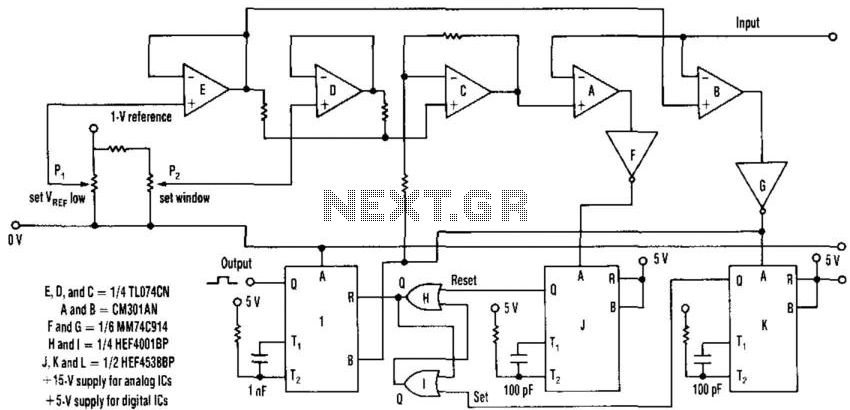

This circuit generates a TTL-compatible pulse whenever the signal falls within the limits established by the potentiometers. The circuit's configuration can be adjusted to suit specific applications. Operational amplifiers E, D, and C are utilized alongside the two potentiometers to provide reference voltages derived from a 1-V precision source for two additional operational amplifiers (A and B) configured as voltage comparators. The input signal is directed to the negative inputs of both comparators. Operational amplifier C is configured as a non-inverting summing amplifier, which is used to derive the higher reference voltage, thereby establishing the acceptance window. Given that the voltage across potentiometer P2 is 0.5 V, the window can be set between 0 and 0.5 V above the value selected for the lower reference level, which is determined by potentiometer P1. The outputs from the comparators are routed to the inputs of inverting Schmitt triggers F and G. Although these triggers operate from a 5-V supply, they feature an extended input voltage range and can accommodate the output voltage swings from the comparators. Two monostable multivibrators, J and K, are triggered on the rising edge of the Schmitt outputs. Monostable J sets and resets the bistable latch formed by two NOR gates. The latch output Q controls the reset of output monostable L, which can only be triggered if its input goes low, derived from the output of G, while its reset condition remains high. According to the timing diagram, when the input signal exceeds the lower reference level, the latch is set, and Q transitions high. When the higher reference level is surpassed, the latch is reset, causing Q to transition low. If only the lower reference level is exceeded, the latch will be set, and monostable L is triggered when the output of G goes low. In scenarios where both reference levels are exceeded, the latch is first set and then reset. However, when G's output goes low, it will not trigger the monostable because its reset condition is low. This circuit is designed for a bandwidth-limited input signal range of 500 to 5,000 Hz with an amplitude range of ±1 V. Adjustments can be made to accommodate different frequency and amplitude ranges.

The circuit operates by utilizing a combination of operational amplifiers and comparators to create a robust signal processing system. The two potentiometers allow for fine-tuning of the reference voltages, providing flexibility for various applications. The operational amplifiers (A and B) serve as voltage comparators, comparing the incoming signal against the established reference levels. The use of a non-inverting summing amplifier (C) to derive the higher reference voltage is critical for establishing the acceptance window, which determines the thresholds for signal detection.

The Schmitt triggers (F and G) play a vital role in ensuring clean transitions between high and low states, effectively filtering out noise from the comparator outputs. This feature is particularly important in environments where signal integrity is paramount. The use of monostable multivibrators (J and K) allows for precise timing control, enabling the circuit to respond accurately to the changes in input signal conditions. The bistable latch formed by the NOR gates adds another layer of control, ensuring that the circuit behaves predictably during state changes.

Overall, this circuit is well-suited for applications requiring precise signal detection and processing, such as in communication systems, sensor interfaces, or data acquisition systems. Its ability to handle a range of frequencies and amplitudes makes it a versatile solution for various electronic design challenges. Modifications can be implemented easily to adapt to different operational parameters, further enhancing its utility in diverse applications. This circuit outputs a TTL-compatible - pulse whenever the signal falls within the limits set by potentiometers and can be varied to suit the application. Op amps, E, D, and C are used with the two potentiometers to supply reference voltages, derived from a 1-V precision source, for two other op amps (A and B) configured as voltage comparators. The input signal is taken to the negative inputs of both these comparators. C is wired as a noninverting summing amp, used to derive the higher reference voltage. Consequently, the acceptance window is set. Because the voltage across potentiometer P2 is 0.5 V, the window can be set between 0 and 0.5 V above the value chosen for the lower reference value.

The lower value is set by PI. The outputs from the comparators are sent to the inputs of inverting Schmitt triggers F and G. Although these triggers operate from a 5-V supply, they have an extended input-voltage range and are capable of handling the comparator"s output voltage swings. The two monostables, J and K, are triggered on the rising edge of the Schmitt outputs. J and set and reset the bistable latch formed by two NOR gates. Latch output Q controls the reset of output monostable L, which can only be triggered if its input goes low, taken from the output of G, while its reset is high.

From the timing diagram, when the signal input exceeds the lower reference level, the latch is set and Q goes high. When the higher reference level is exceeded, the latch is reset and Q goes low. If only the lower reference is exceeded, the latch will be set and L is triggered when G"s output goes low.

When both levels are exceeded, the latch is set, then reset. When G"s output goes low, it won"t trigger the mono-stable because its reset is low. The circuit, as shown, was used for a bandwidth-limited, 500- to 5 000 Hz input signal with an amplitude range of ± 1 V. Modifications can easily be made to cover other frequency and amplitude ranges. 🔗 External reference

The circuit operates by utilizing a combination of operational amplifiers and comparators to create a robust signal processing system. The two potentiometers allow for fine-tuning of the reference voltages, providing flexibility for various applications. The operational amplifiers (A and B) serve as voltage comparators, comparing the incoming signal against the established reference levels. The use of a non-inverting summing amplifier (C) to derive the higher reference voltage is critical for establishing the acceptance window, which determines the thresholds for signal detection.

The Schmitt triggers (F and G) play a vital role in ensuring clean transitions between high and low states, effectively filtering out noise from the comparator outputs. This feature is particularly important in environments where signal integrity is paramount. The use of monostable multivibrators (J and K) allows for precise timing control, enabling the circuit to respond accurately to the changes in input signal conditions. The bistable latch formed by the NOR gates adds another layer of control, ensuring that the circuit behaves predictably during state changes.

Overall, this circuit is well-suited for applications requiring precise signal detection and processing, such as in communication systems, sensor interfaces, or data acquisition systems. Its ability to handle a range of frequencies and amplitudes makes it a versatile solution for various electronic design challenges. Modifications can be implemented easily to adapt to different operational parameters, further enhancing its utility in diverse applications. This circuit outputs a TTL-compatible - pulse whenever the signal falls within the limits set by potentiometers and can be varied to suit the application. Op amps, E, D, and C are used with the two potentiometers to supply reference voltages, derived from a 1-V precision source, for two other op amps (A and B) configured as voltage comparators. The input signal is taken to the negative inputs of both these comparators. C is wired as a noninverting summing amp, used to derive the higher reference voltage. Consequently, the acceptance window is set. Because the voltage across potentiometer P2 is 0.5 V, the window can be set between 0 and 0.5 V above the value chosen for the lower reference value.

The lower value is set by PI. The outputs from the comparators are sent to the inputs of inverting Schmitt triggers F and G. Although these triggers operate from a 5-V supply, they have an extended input-voltage range and are capable of handling the comparator"s output voltage swings. The two monostables, J and K, are triggered on the rising edge of the Schmitt outputs. J and set and reset the bistable latch formed by two NOR gates. Latch output Q controls the reset of output monostable L, which can only be triggered if its input goes low, taken from the output of G, while its reset is high.

From the timing diagram, when the signal input exceeds the lower reference level, the latch is set and Q goes high. When the higher reference level is exceeded, the latch is reset and Q goes low. If only the lower reference is exceeded, the latch will be set and L is triggered when G"s output goes low.

When both levels are exceeded, the latch is set, then reset. When G"s output goes low, it won"t trigger the mono-stable because its reset is low. The circuit, as shown, was used for a bandwidth-limited, 500- to 5 000 Hz input signal with an amplitude range of ± 1 V. Modifications can easily be made to cover other frequency and amplitude ranges. 🔗 External reference

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713