Low frequency oscillator-flasher

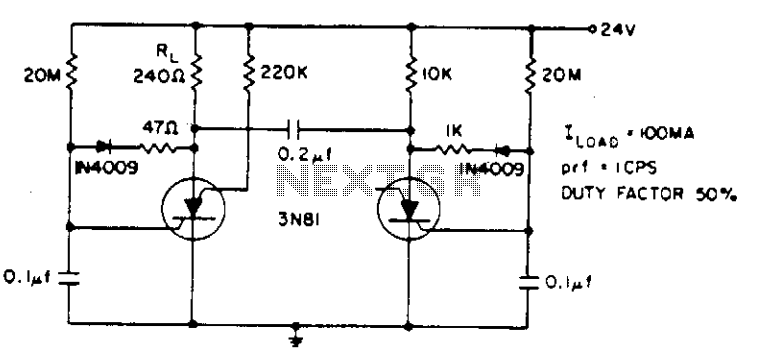

Electrolytic capacitors are not required to generate a 1 cps frequency. When the silicon-controlled switch (SCS) is triggered, the 0.2 µF commutating capacitor deactivates the other capacitor and charges its gate capacitor to a negative potential. The gate capacitor charges to 24 volts through a resistor, retriggering the SCS. Battery power is supplied to the load with an efficiency of 88%. The resistors can be adjusted to modify the pulse repetition frequency (PRF) or duty cycle.

The circuit described operates effectively without the need for electrolytic capacitors, which are typically used in timing and filtering applications. The use of a 0.2 µF commutating capacitor plays a critical role in the switching mechanism of the SCS. Upon triggering, this capacitor discharges, causing the SCS to turn off the other capacitor in the circuit, which is essential for maintaining the desired operation of the system.

The gate capacitor, which is charged to a negative potential, is pivotal for controlling the SCS. The charging process occurs through a resistor, allowing the gate capacitor to reach a voltage of 24 volts. This voltage level is crucial as it retriggers the SCS, ensuring that the circuit continues to operate as intended.

The efficiency of 88% in delivering battery power to the load indicates a well-designed circuit that minimizes energy losses. This efficiency can be attributed to the careful selection of components and the design of the switching mechanism.

Furthermore, the ability to vary the resistors within the circuit provides flexibility in adjusting the pulse repetition frequency (PRF) and the duty cycle. This feature allows for customization based on the application's requirements, enabling the circuit to adapt to different operational conditions. By changing the resistance values, the timing characteristics of the circuit can be modified, which is crucial for applications requiring precise control over frequency and duty factor.

Overall, this circuit design demonstrates a robust approach to managing power delivery and timing without the need for traditional electrolytic capacitors, thus enhancing reliability and performance.Electrolytic capacitors are unnecessary to generate a 1 cps frequency. As an scs triggers on, the 0.2 µ¥ commutating capacitor turns off the other one and charges its gate capacitor to a negative potential. The gate capacitor charges towards 24 volts through 20 retriggering its scs. Battery power is delivered to the load with 88% efficiency. The 20 resistors can be varied to change prf or duty factor.

The circuit described operates effectively without the need for electrolytic capacitors, which are typically used in timing and filtering applications. The use of a 0.2 µF commutating capacitor plays a critical role in the switching mechanism of the SCS. Upon triggering, this capacitor discharges, causing the SCS to turn off the other capacitor in the circuit, which is essential for maintaining the desired operation of the system.

The gate capacitor, which is charged to a negative potential, is pivotal for controlling the SCS. The charging process occurs through a resistor, allowing the gate capacitor to reach a voltage of 24 volts. This voltage level is crucial as it retriggers the SCS, ensuring that the circuit continues to operate as intended.

The efficiency of 88% in delivering battery power to the load indicates a well-designed circuit that minimizes energy losses. This efficiency can be attributed to the careful selection of components and the design of the switching mechanism.

Furthermore, the ability to vary the resistors within the circuit provides flexibility in adjusting the pulse repetition frequency (PRF) and the duty cycle. This feature allows for customization based on the application's requirements, enabling the circuit to adapt to different operational conditions. By changing the resistance values, the timing characteristics of the circuit can be modified, which is crucial for applications requiring precise control over frequency and duty factor.

Overall, this circuit design demonstrates a robust approach to managing power delivery and timing without the need for traditional electrolytic capacitors, thus enhancing reliability and performance.Electrolytic capacitors are unnecessary to generate a 1 cps frequency. As an scs triggers on, the 0.2 µ¥ commutating capacitor turns off the other one and charges its gate capacitor to a negative potential. The gate capacitor charges towards 24 volts through 20 retriggering its scs. Battery power is delivered to the load with 88% efficiency. The 20 resistors can be varied to change prf or duty factor.