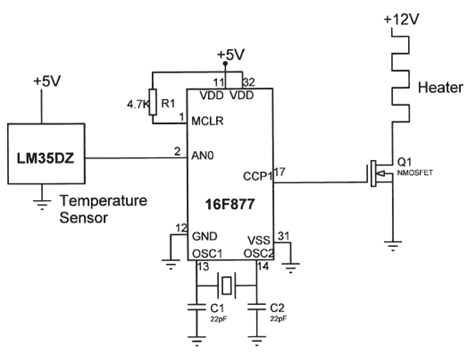

Low-Level Power Fet Driver Method

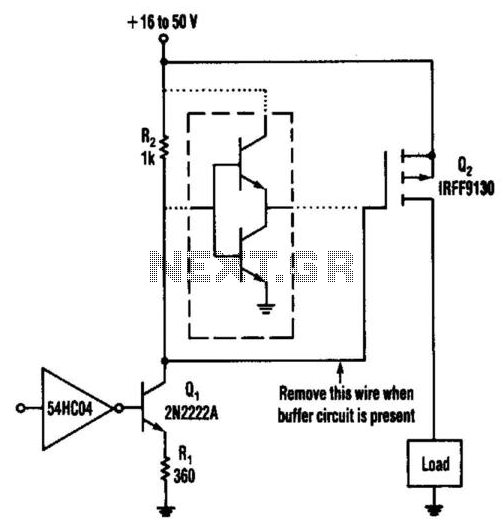

This circuit operates from a 16- to 50-V supply. Adding the buffer circuit (within the dashed lines) offers 100-ns switching times. Otherwise, the circuit switches in 1 µs. Q1 and R1 form a switched current source of about 12 mA. The current flows through R2, which supplies 12 V to the FET. The circuit works well over a wide range of supply voltages. Furthermore, it switches smoothly in the presence of large ripple and noise on the supply. The switching time (about 1 µs) can be reduced considerably by lowering the values of R1 and R2 at the expense of higher power dissipation in the resistors and Q1. Alternatively, a buffer circuit can be added to produce switching times of 100 ns without generating significant power dissipation.

This circuit is designed to operate within a voltage range of 16 to 50 volts, making it versatile for various applications. The inclusion of a buffer circuit, indicated within the dashed lines in the schematic, enhances the performance by achieving switching times as low as 100 nanoseconds. In its standard configuration, the circuit achieves a switching time of approximately 1 microsecond, which is adequate for many applications but can be improved.

The core of the circuit consists of a transistor (Q1) and a resistor (R1), which together function as a switched current source. This current source is capable of delivering around 12 milliamperes (mA) to the load. The current then passes through another resistor (R2), which regulates the voltage supplied to the field-effect transistor (FET) at 12 volts. This configuration allows the circuit to maintain stable operation across a broad spectrum of supply voltages, ensuring reliable performance even in the presence of significant voltage ripple and noise.

To optimize the switching time, it is possible to reduce the values of resistors R1 and R2. However, this modification comes with a trade-off, as it results in increased power dissipation within both the resistors and the transistor Q1. Therefore, careful consideration must be given to the thermal management of these components when adjusting their values.

Alternatively, the implementation of a buffer circuit can significantly enhance the switching speed to 100 nanoseconds while maintaining low power dissipation levels. This is particularly advantageous in applications where rapid switching is critical, and power efficiency is a concern. Overall, this circuit design provides a robust solution for applications requiring reliable switching performance across varying supply conditions. This circuit operates from a 16- to 50-V supply. Adding the buffer circuit (within the dashed lines) offe rs 100-ns switching times. Otherwise, the circuit switches in 1 /xs. Ql and R1 form a switched current source of about 12 mA. The current flows through R2, which supplies 12 V to the FET. The circuit works well over a wide range of supply voltages. Furthermore, it switches smoothly in the presence of large ripple and noise on the supply. The switching time (about 1 /as) can be reduced considerably by lowering the values of Ri and R2 at the expense of higher power dissipations in the resistors and Ql. Alternatively, a buffer circuit can be added to produce switching times of 100 ns without generating significant power dissipation.

🔗 External reference

This circuit is designed to operate within a voltage range of 16 to 50 volts, making it versatile for various applications. The inclusion of a buffer circuit, indicated within the dashed lines in the schematic, enhances the performance by achieving switching times as low as 100 nanoseconds. In its standard configuration, the circuit achieves a switching time of approximately 1 microsecond, which is adequate for many applications but can be improved.

The core of the circuit consists of a transistor (Q1) and a resistor (R1), which together function as a switched current source. This current source is capable of delivering around 12 milliamperes (mA) to the load. The current then passes through another resistor (R2), which regulates the voltage supplied to the field-effect transistor (FET) at 12 volts. This configuration allows the circuit to maintain stable operation across a broad spectrum of supply voltages, ensuring reliable performance even in the presence of significant voltage ripple and noise.

To optimize the switching time, it is possible to reduce the values of resistors R1 and R2. However, this modification comes with a trade-off, as it results in increased power dissipation within both the resistors and the transistor Q1. Therefore, careful consideration must be given to the thermal management of these components when adjusting their values.

Alternatively, the implementation of a buffer circuit can significantly enhance the switching speed to 100 nanoseconds while maintaining low power dissipation levels. This is particularly advantageous in applications where rapid switching is critical, and power efficiency is a concern. Overall, this circuit design provides a robust solution for applications requiring reliable switching performance across varying supply conditions. This circuit operates from a 16- to 50-V supply. Adding the buffer circuit (within the dashed lines) offe rs 100-ns switching times. Otherwise, the circuit switches in 1 /xs. Ql and R1 form a switched current source of about 12 mA. The current flows through R2, which supplies 12 V to the FET. The circuit works well over a wide range of supply voltages. Furthermore, it switches smoothly in the presence of large ripple and noise on the supply. The switching time (about 1 /as) can be reduced considerably by lowering the values of Ri and R2 at the expense of higher power dissipations in the resistors and Ql. Alternatively, a buffer circuit can be added to produce switching times of 100 ns without generating significant power dissipation.

🔗 External reference