Many space impulses generating circuit on the basis of one-chip computer and CPLD

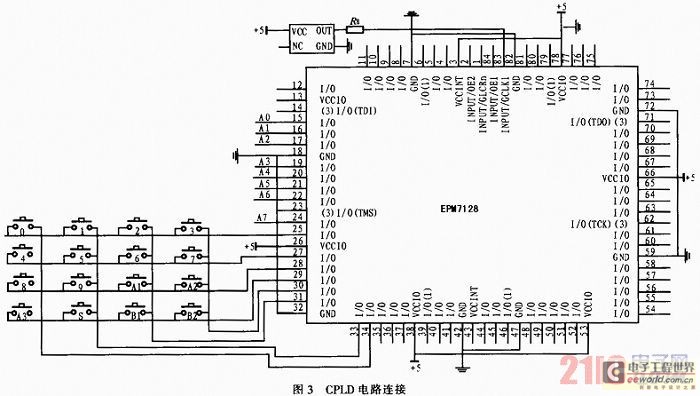

The system utilizes a modular design featuring the AT89S52 microcontroller and CPLD as the central processing unit (CPU) for overall system coordination. Initially, it establishes a cycle of systematic pulse signals through a 4G-4 key set module, allowing for the selection of pulse output modes and providing status indications. The CPLD communicates data with the microcontroller after receiving an input signal, and it displays pulse video intervals on an LCD1602. The data processing between the microcontroller and CPLD generates the required pulse signal, which is output by the CPLD. Status indications are provided by three different colored LEDs (red, green, yellow) sourced from the I/O outputs of the CPLD. The first ten keys of the 4G-4 key set module correspond to figures 0-9, the 11th key represents the radix point, the 12th key is the options button A1 for pulse selection, and the 13th and 14th keys are A2 and A3 for choosing the output modes (single head, bipitch, three). An additional YES key is included. The AT89S52 is a low-power, high-performance microcontroller with 8 kB of programmable flash memory. It employs non-volatile memory technology from Atmel, ensuring full compatibility with industry-standard 80C51 products in terms of order and pin configuration. The flash memory allows for programmable storage within the system and is compatible with standard programmers. The AT89S52 features 8 versatile CPUs, providing a flexible and effective solution for numerous embedded applications. Its standard functions include 8 kB of flash memory, 256 bytes of RAM, 32 I/O ports, a watchdog timer, two data indicators, three 16-bit timers/counters, a 6-vector interrupt structure, and a full-duplex serial port, along with an on-chip clock circuit. Additionally, the AT89S52 can operate at 0 Hz in static logic mode and supports two software selectable power-saving modes. In idle mode, the CPU halts operations while allowing RAM, timers/counters, and the serial port to cease functioning. In power-down mode, RAM content is preserved while all operations of the microcontroller are suspended until power is restored or hardware is reset. The EPM7128SLC84 is a CPLD device developed by Altera, part of the MAX series 7000S. It features high-density PLD integration and is one of the fastest types in the series, utilizing the second-generation MAX Multiple Array Matrix Structure. Its design includes serial metal wiring for interconnections, minimizing signal delay and enhancing chip resource utilization. The EPM7128SLC84 is a programmable CMOS device based on EEPROM technology.

The modular design of the system allows for scalability and flexibility in various applications. The AT89S52 microcontroller, with its 8 kB of flash memory and 256 bytes of RAM, provides ample resources for executing complex algorithms and managing multiple I/O operations. The CPLD, EPM7128SLC84, enhances the system's capability by facilitating efficient data handling and signal processing, ensuring that pulse signals are generated accurately and with minimal delay.

The 4G-4 key set module serves as a user interface, enabling users to interact with the system effectively. The color-coded LED indicators provide immediate feedback on the system's status, enhancing usability. The choice of pulse output modes allows for versatility in applications, catering to different operational requirements.

The integration of power-saving modes in the AT89S52 microcontroller is particularly beneficial for battery-operated devices, extending operational life while maintaining performance. The ability to retain RAM content during power-down mode ensures that critical data is not lost, allowing for quick recovery and continued operation when power is restored.

Overall, this system architecture exemplifies a well-thought-out combination of components that work harmoniously to deliver reliable performance in embedded applications, with an emphasis on user interaction, power efficiency, and processing capability.The system adopts the modular design, the one-chip computer AT89S52 and CPLD is CPU of the overall system, the coordination of the control system. Set up the cycle of the systematic pulse signal through 4G—4 key set module at first, choose the output mode of the pulse, and provide status indication; CPLD carries on data communication with the one-chip computer after receiving the input signal,

and reveal pulse video interval through LCD1602, then pass the data processing of one-chip computer and CPLD and produce the required pulse signal, exported by CPLD. Among them status indication is red, green, yellow by 3 different colors Luminescent diode provide, its level is from I/0 mouth output of CPLD; The first 10 locations of the key of 4G—4 key set module keyboard are that figures 0-9, 11th are that radix point, the 12th are the options button A1 of the pulse to the 14th, A2, A3 is used for choosing the output mode single head, bipitch, three, Add another YES key.

AT89S52 is a kind of low power consumption, 8 high-performance microcontrollers, have 8 k bytes in the programmable Flash memorizer of the system. AT89S52 uses the nonvolatile memory technology of the high density of Atmel Company to make, fully compatible with industry 80C51 products order and pin.

Flash allows the programm store programmably in the system, is also suitable for the regular programmer on slice. On the single chip, AT89S52 has 8 dexterous CPUs and in the system programmable Flash, make AT89S52 control the application system to offer the high flexible, valid solution for being numerous and embedded.

AT89S52 has the following standard functions: 8 k byte Flash, 256 bytes RAM, 32-bit microcomputer I/O port line, watchdog`s timer, 2 data indicators, 3 16 timers / counters, a 6 vector and 2 grades of interrupt structures, the serial port of full duplex, the Jingzhen and clock circuit on-chip. In addition, AT89S52 can be dropped to 0 Hz static logic operation, supporting 2 kinds of software can be chosen the Power Save Mode.

Under the idle mode, CPU inoperation, allow RAM, timer / counter, serial port to stop continuing working. Under the guard mode of the power down, RAM content is kept, the Shaker is frozen, all work of one-chip computer stops, until the next one cuts off or the hardware is reset.

EPM7128SLC84 is CPLD device that Altera Company develops, it is MAX series 7000S. In device, PLD of high integration density, MAX7000S the intersection of speed and most quick type one of in series, it second generation MAX MultipleArray Matrix Structure. Besides high advantage of the integrated level, the unit cell within the device Between connection last metal wire that is serial, for signal channels at time delay stationary short will be offered between unitting in kinds of interconnection structure, thus has dispelled the delayed difficult predicting of inside, and raised the utilization efficiency of chip resources effectively.

EPM7128SLC84 is a programmable CMOS device based on EEPROM, its main performance index is: The external 🔗 External reference

The modular design of the system allows for scalability and flexibility in various applications. The AT89S52 microcontroller, with its 8 kB of flash memory and 256 bytes of RAM, provides ample resources for executing complex algorithms and managing multiple I/O operations. The CPLD, EPM7128SLC84, enhances the system's capability by facilitating efficient data handling and signal processing, ensuring that pulse signals are generated accurately and with minimal delay.

The 4G-4 key set module serves as a user interface, enabling users to interact with the system effectively. The color-coded LED indicators provide immediate feedback on the system's status, enhancing usability. The choice of pulse output modes allows for versatility in applications, catering to different operational requirements.

The integration of power-saving modes in the AT89S52 microcontroller is particularly beneficial for battery-operated devices, extending operational life while maintaining performance. The ability to retain RAM content during power-down mode ensures that critical data is not lost, allowing for quick recovery and continued operation when power is restored.

Overall, this system architecture exemplifies a well-thought-out combination of components that work harmoniously to deliver reliable performance in embedded applications, with an emphasis on user interaction, power efficiency, and processing capability.The system adopts the modular design, the one-chip computer AT89S52 and CPLD is CPU of the overall system, the coordination of the control system. Set up the cycle of the systematic pulse signal through 4G—4 key set module at first, choose the output mode of the pulse, and provide status indication; CPLD carries on data communication with the one-chip computer after receiving the input signal,

and reveal pulse video interval through LCD1602, then pass the data processing of one-chip computer and CPLD and produce the required pulse signal, exported by CPLD. Among them status indication is red, green, yellow by 3 different colors Luminescent diode provide, its level is from I/0 mouth output of CPLD; The first 10 locations of the key of 4G—4 key set module keyboard are that figures 0-9, 11th are that radix point, the 12th are the options button A1 of the pulse to the 14th, A2, A3 is used for choosing the output mode single head, bipitch, three, Add another YES key.

AT89S52 is a kind of low power consumption, 8 high-performance microcontrollers, have 8 k bytes in the programmable Flash memorizer of the system. AT89S52 uses the nonvolatile memory technology of the high density of Atmel Company to make, fully compatible with industry 80C51 products order and pin.

Flash allows the programm store programmably in the system, is also suitable for the regular programmer on slice. On the single chip, AT89S52 has 8 dexterous CPUs and in the system programmable Flash, make AT89S52 control the application system to offer the high flexible, valid solution for being numerous and embedded.

AT89S52 has the following standard functions: 8 k byte Flash, 256 bytes RAM, 32-bit microcomputer I/O port line, watchdog`s timer, 2 data indicators, 3 16 timers / counters, a 6 vector and 2 grades of interrupt structures, the serial port of full duplex, the Jingzhen and clock circuit on-chip. In addition, AT89S52 can be dropped to 0 Hz static logic operation, supporting 2 kinds of software can be chosen the Power Save Mode.

Under the idle mode, CPU inoperation, allow RAM, timer / counter, serial port to stop continuing working. Under the guard mode of the power down, RAM content is kept, the Shaker is frozen, all work of one-chip computer stops, until the next one cuts off or the hardware is reset.

EPM7128SLC84 is CPLD device that Altera Company develops, it is MAX series 7000S. In device, PLD of high integration density, MAX7000S the intersection of speed and most quick type one of in series, it second generation MAX MultipleArray Matrix Structure. Besides high advantage of the integrated level, the unit cell within the device Between connection last metal wire that is serial, for signal channels at time delay stationary short will be offered between unitting in kinds of interconnection structure, thus has dispelled the delayed difficult predicting of inside, and raised the utilization efficiency of chip resources effectively.

EPM7128SLC84 is a programmable CMOS device based on EEPROM, its main performance index is: The external 🔗 External reference