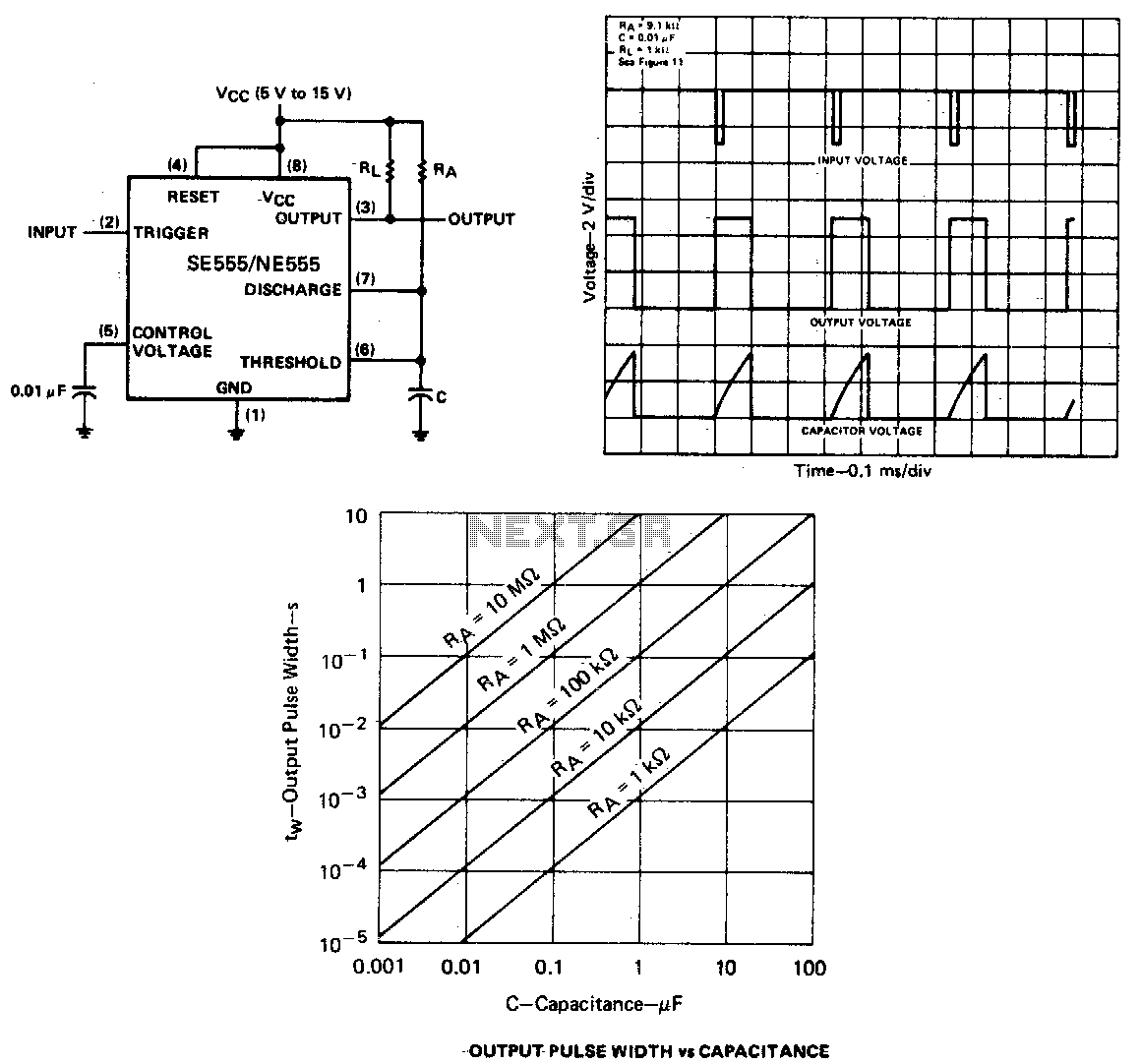

Monostable circuit

When the output is low, applying a negative-going pulse to the trigger input sets the flip-flop (Q goes low), driving the output high and turning off component 1. Capacitor C is then charged through resistor Ra until the voltage across the capacitor reaches the threshold voltage of the threshold input. If the trigger input has returned to a high level, the output of the threshold comparator will reset the flip-flop (Q goes high), driving the output low and discharging capacitor C through transistor Q1. Monostable operation is initiated when the trigger input voltage falls below the trigger threshold. Once initiated, the sequence will complete only if the trigger input remains high at the end of the timing interval.

The described circuit primarily utilizes a flip-flop configuration, which is essential for creating a monostable multivibrator. In this setup, the flip-flop serves as the core timing element. The trigger input is crucial for initiating the timing cycle; when a negative pulse is applied, it switches the state of the flip-flop, causing Q to transition low. This transition activates the output, which can drive subsequent components or systems.

Capacitor C, in conjunction with resistor Ra, forms an RC timing network that determines the duration of the output pulse. The charging of capacitor C continues until the voltage across it reaches a predefined threshold. This threshold is critical as it dictates when the threshold comparator will act to reset the flip-flop.

Once the trigger input returns to a high state, the threshold comparator responds by resetting the flip-flop, which in turn causes Q to go high. This transition results in the output being driven low and initiates the discharge of capacitor C through transistor Q1. The timing interval is thus defined by the RC time constant, which is influenced by the values of resistor Ra and capacitor C.

The circuit's behavior ensures that the monostable operation is contingent upon the trigger input remaining high at the conclusion of the timing interval. If the trigger input does not meet this condition, the timing sequence will not complete, demonstrating the circuit's reliance on precise input conditions for proper functionality. This design is commonly used in applications requiring pulse generation, timing, and control sequences in electronic systems.If the output is low, application of a negative-going pulse to the trigger input sets the flip-flop (Q goes low), drives the output high, and turns off 1. Capacitor C is then charged through Ra until the voltage across the capacitor reaches the threshold voltage of the threshold input.

If the trigger input has returned to a high level, the output of the threshold comparator will reset the flip-flop (Q goes high), drive the output low, and discharge C through Ql Monostable operations is initiated when the trigger input voltage falls below the trigger threshold. Once initiated, the sequence will complete only if the trigger input is high at the end of the timing interval. 🔗 External reference

The described circuit primarily utilizes a flip-flop configuration, which is essential for creating a monostable multivibrator. In this setup, the flip-flop serves as the core timing element. The trigger input is crucial for initiating the timing cycle; when a negative pulse is applied, it switches the state of the flip-flop, causing Q to transition low. This transition activates the output, which can drive subsequent components or systems.

Capacitor C, in conjunction with resistor Ra, forms an RC timing network that determines the duration of the output pulse. The charging of capacitor C continues until the voltage across it reaches a predefined threshold. This threshold is critical as it dictates when the threshold comparator will act to reset the flip-flop.

Once the trigger input returns to a high state, the threshold comparator responds by resetting the flip-flop, which in turn causes Q to go high. This transition results in the output being driven low and initiates the discharge of capacitor C through transistor Q1. The timing interval is thus defined by the RC time constant, which is influenced by the values of resistor Ra and capacitor C.

The circuit's behavior ensures that the monostable operation is contingent upon the trigger input remaining high at the conclusion of the timing interval. If the trigger input does not meet this condition, the timing sequence will not complete, demonstrating the circuit's reliance on precise input conditions for proper functionality. This design is commonly used in applications requiring pulse generation, timing, and control sequences in electronic systems.If the output is low, application of a negative-going pulse to the trigger input sets the flip-flop (Q goes low), drives the output high, and turns off 1. Capacitor C is then charged through Ra until the voltage across the capacitor reaches the threshold voltage of the threshold input.

If the trigger input has returned to a high level, the output of the threshold comparator will reset the flip-flop (Q goes high), drive the output low, and discharge C through Ql Monostable operations is initiated when the trigger input voltage falls below the trigger threshold. Once initiated, the sequence will complete only if the trigger input is high at the end of the timing interval. 🔗 External reference