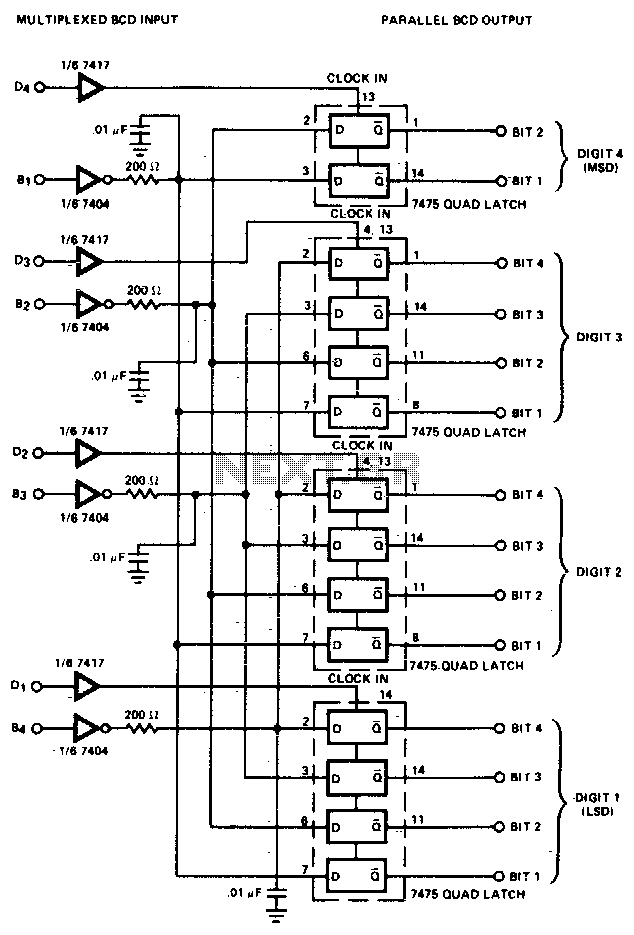

Multiplexed bcd-to-parallel bcd converter

The converter is composed of four quad bistable latches that are activated in the correct sequence by the digit strobe output from the LD110. The complemented outputs (Q) of the quad latch set represent the state of the bit outputs when the digit strobe signal transitions to a high state. This state is preserved when the digit strobe signal returns to a low state.

The converter utilizes four quad bistable latches, each capable of storing a single bit of information. These latches are arranged in a manner that allows them to be triggered sequentially by the digit strobe output from the LD110, which serves as a timing reference for the operation. When the digit strobe signal transitions from low to high, it activates the latches, causing them to capture and reflect the current state of the bit outputs. This operation is crucial for applications requiring precise timing and data integrity.

The complemented outputs (Q) provide an inverted representation of the stored data, enabling easy interfacing with other digital components that may require active-low signals. Once the digit strobe signal goes low, the latches maintain their last captured state, ensuring that the data remains stable and unaffected by further changes in the strobe signal. This feature is particularly important in digital systems where data consistency must be preserved during processing cycles.

In terms of circuit design, the layout would typically include power supply connections, ground, and appropriate signal routing to ensure that the strobe signal reaches all latches simultaneously. Additional components such as pull-up or pull-down resistors may be incorporated to enhance signal integrity and prevent floating states during transitions. The overall design should also consider the propagation delay of the latches to ensure that the timing of the digit strobe signal aligns with the desired operation of the system.Converter consists of four quad bistable latches activated in the proper sequence by the digit strobe output of the LD110. The complemented outputs (Q) of the quad latch set reflects the state of the bit outputs when the digit strobe goes high.

It will maintain this state when the digit strobe goes low. 🔗 External reference

The converter utilizes four quad bistable latches, each capable of storing a single bit of information. These latches are arranged in a manner that allows them to be triggered sequentially by the digit strobe output from the LD110, which serves as a timing reference for the operation. When the digit strobe signal transitions from low to high, it activates the latches, causing them to capture and reflect the current state of the bit outputs. This operation is crucial for applications requiring precise timing and data integrity.

The complemented outputs (Q) provide an inverted representation of the stored data, enabling easy interfacing with other digital components that may require active-low signals. Once the digit strobe signal goes low, the latches maintain their last captured state, ensuring that the data remains stable and unaffected by further changes in the strobe signal. This feature is particularly important in digital systems where data consistency must be preserved during processing cycles.

In terms of circuit design, the layout would typically include power supply connections, ground, and appropriate signal routing to ensure that the strobe signal reaches all latches simultaneously. Additional components such as pull-up or pull-down resistors may be incorporated to enhance signal integrity and prevent floating states during transitions. The overall design should also consider the propagation delay of the latches to ensure that the timing of the digit strobe signal aligns with the desired operation of the system.Converter consists of four quad bistable latches activated in the proper sequence by the digit strobe output of the LD110. The complemented outputs (Q) of the quad latch set reflects the state of the bit outputs when the digit strobe goes high.

It will maintain this state when the digit strobe goes low. 🔗 External reference