No linear feedback amplifier circuit a

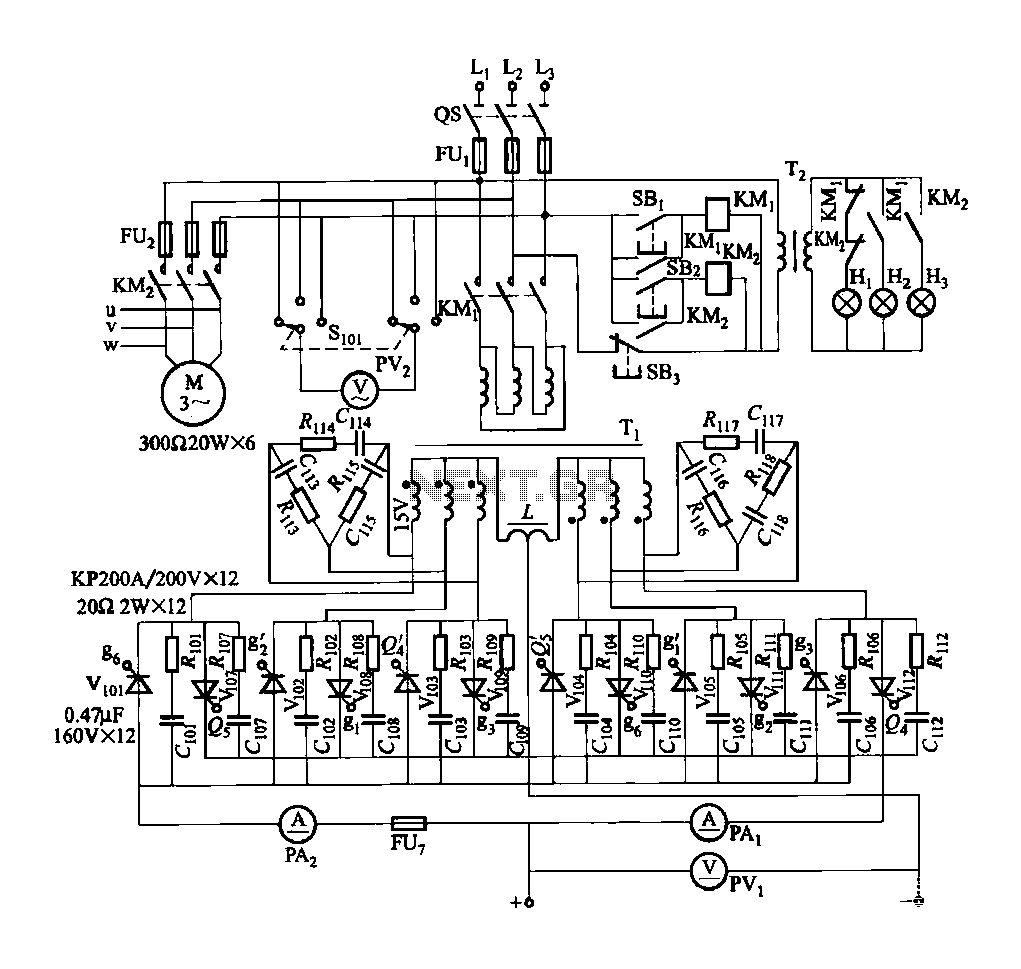

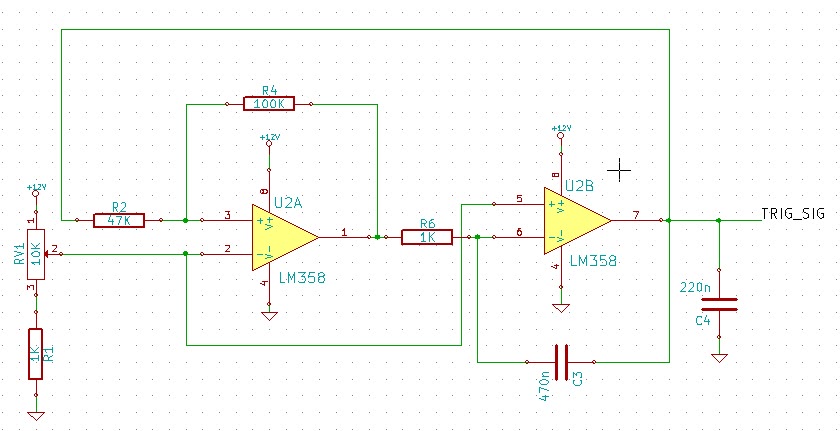

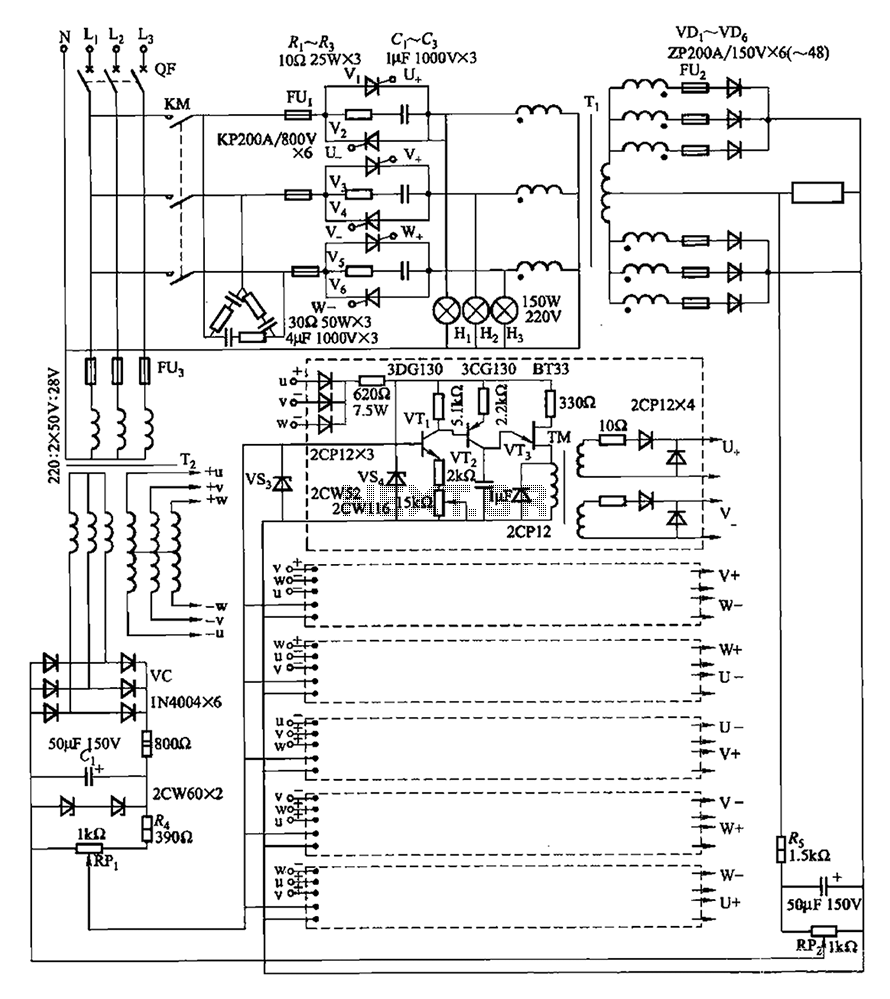

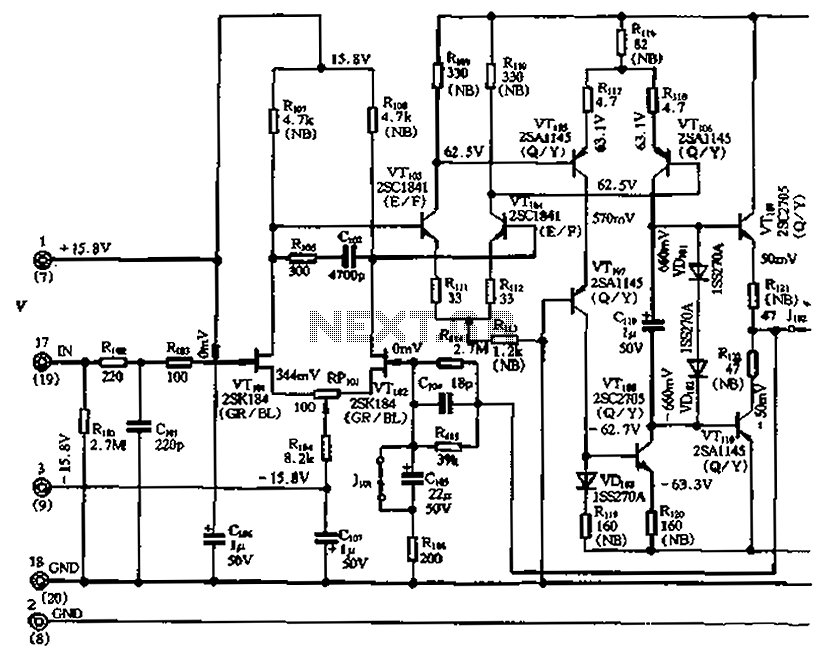

The circuit features a differential input stage that implements differential voltage amplification, forced differential voltage amplification, and a complementary push-pull amplifier output. It includes a bias circuit, a distortion servo circuit, and a protection circuit. The input preamplifier stage is illustrated in Figure 2-41 (a), which utilizes a FET differential input circuit composed of VTioi and VTloz. The high input impedance of the FET minimizes the input capacitance, resulting in a true DC amplifier circuit. The low-voltage FET operates on a single low-voltage power supply of -15V to +8V, employing a 9mΩ high FET for Rcos. The phase compensation circuit, C102, is implemented to prevent excessive signal distortion due to high stop rates. The differential voltage amplifier stage is formed by VTi and VT04, providing sufficient gain to drive a forced balanced differential amplifier stage, which operates at a larger current of approximately 4mA. The circuit formed by VTios and VTios demonstrates excellent performance as a forced balanced differential amplifier. This design effectively addresses the electrical effects of voltage changes in the differential circuit, while simplifying the circuit design to enhance gain and reduce distortion. The collector of VTios connects to L07, which constitutes a common-emitter amplifier circuit group, improving linearity and bandwidth. The addition of VTll07 results in a set level with zero equivalent capacitance, significantly reducing distortion. The buffer amplifier stage is formed by VT109 and VTiio, while VDiot and VD102 serve as the base bias circuit, providing a bias current of approximately 1mA. The stabilizing capacitor, cII, bypasses the AC component of the collector current of VT106, maintaining a constant output level and facilitating the distortion correction circuit.

The described circuit is a sophisticated arrangement designed to achieve high-performance differential voltage amplification. The differential input stage is crucial for processing small signal variations while rejecting common-mode noise effectively. The use of FETs in the input stage is advantageous due to their high input impedance, which allows for minimal loading on the preceding circuit and improves overall signal integrity.

The forced differential voltage amplification stage enhances the circuit's ability to maintain linearity and reduce distortion, which is vital in applications requiring high fidelity. The design incorporates a bias circuit that stabilizes the operating point of the amplifiers, ensuring consistent performance across varying input conditions. The distortion servo circuit actively monitors and corrects any deviations from the desired output, further enhancing the fidelity of the amplification process.

The common-emitter amplifier configuration provides additional gain and improves the bandwidth of the circuit. The inclusion of phase compensation through capacitor C102 is essential to mitigate potential stability issues that could arise from high-frequency signals. The careful selection of components ensures that the circuit remains robust against variations in supply voltage and temperature, thus maintaining performance over a wide range of operating conditions.

Overall, this circuit exemplifies a well-engineered approach to differential amplification, balancing performance, stability, and simplicity, making it suitable for a variety of electronic applications, including audio processing, sensor signal conditioning, and instrumentation. By the differential input stage, a differential voltage amplification, a forced differential voltage amplification, slow punch amplified complementary push-pull amplifier outpu t bias circuit, distortion servo circuit and protection circuit. Figure 2-41 (a) for the input preamplifier stage. VTioi, VTloz composition FET differential input circuit. Due to the high input impedance FET input for the omitted input capacitance, a real DC amplifier circuit. Due to the low voltage FET, using a single low-voltage power supply ( 15 -8V), and the use of 9m high FET o Rcos, C102 is a phase compensation circuit, to prevent the stop rate is too high due to the input signal distortion.

VTi, VT04 constitute a differential voltage amplifier stage, to get enough gain to drive to force a balanced differential amplifier stage, this level takes a larger operating current t about 4. SMAO VTios ~ VTios constitute very good performance to force balanced differential amplifier level. This circuit is a good solution to the electrical effect of changes in voltage of the differential circuit, and simple circuit design improves the circuit gain, fork reduces distortion.

In VTios collector access, L07 constitute a common-emitter amplifier circuit group altogether, not only can improve the linearity, wide bandwidth the same time, due VTll07 of access makes this group a set level between zero equivalent capacitance, this greatly reduces the level of distortion. VT109, VTiio constituting a buffer amplifier stage, VDiot, VD102 constitutes its base bias circuit, the present stage to provide a bias current of about ImA o cII (J is the base bias stabilizing capacitor, which makes the collector current VT106 the AC component is bypassed, the bias voltage to maintain the output level constant, and the distortion correction circuit.

The described circuit is a sophisticated arrangement designed to achieve high-performance differential voltage amplification. The differential input stage is crucial for processing small signal variations while rejecting common-mode noise effectively. The use of FETs in the input stage is advantageous due to their high input impedance, which allows for minimal loading on the preceding circuit and improves overall signal integrity.

The forced differential voltage amplification stage enhances the circuit's ability to maintain linearity and reduce distortion, which is vital in applications requiring high fidelity. The design incorporates a bias circuit that stabilizes the operating point of the amplifiers, ensuring consistent performance across varying input conditions. The distortion servo circuit actively monitors and corrects any deviations from the desired output, further enhancing the fidelity of the amplification process.

The common-emitter amplifier configuration provides additional gain and improves the bandwidth of the circuit. The inclusion of phase compensation through capacitor C102 is essential to mitigate potential stability issues that could arise from high-frequency signals. The careful selection of components ensures that the circuit remains robust against variations in supply voltage and temperature, thus maintaining performance over a wide range of operating conditions.

Overall, this circuit exemplifies a well-engineered approach to differential amplification, balancing performance, stability, and simplicity, making it suitable for a variety of electronic applications, including audio processing, sensor signal conditioning, and instrumentation. By the differential input stage, a differential voltage amplification, a forced differential voltage amplification, slow punch amplified complementary push-pull amplifier outpu t bias circuit, distortion servo circuit and protection circuit. Figure 2-41 (a) for the input preamplifier stage. VTioi, VTloz composition FET differential input circuit. Due to the high input impedance FET input for the omitted input capacitance, a real DC amplifier circuit. Due to the low voltage FET, using a single low-voltage power supply ( 15 -8V), and the use of 9m high FET o Rcos, C102 is a phase compensation circuit, to prevent the stop rate is too high due to the input signal distortion.

VTi, VT04 constitute a differential voltage amplifier stage, to get enough gain to drive to force a balanced differential amplifier stage, this level takes a larger operating current t about 4. SMAO VTios ~ VTios constitute very good performance to force balanced differential amplifier level. This circuit is a good solution to the electrical effect of changes in voltage of the differential circuit, and simple circuit design improves the circuit gain, fork reduces distortion.

In VTios collector access, L07 constitute a common-emitter amplifier circuit group altogether, not only can improve the linearity, wide bandwidth the same time, due VTll07 of access makes this group a set level between zero equivalent capacitance, this greatly reduces the level of distortion. VT109, VTiio constituting a buffer amplifier stage, VDiot, VD102 constitutes its base bias circuit, the present stage to provide a bias current of about ImA o cII (J is the base bias stabilizing capacitor, which makes the collector current VT106 the AC component is bypassed, the bias voltage to maintain the output level constant, and the distortion correction circuit.

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713