Non-integer programmable pulse divider

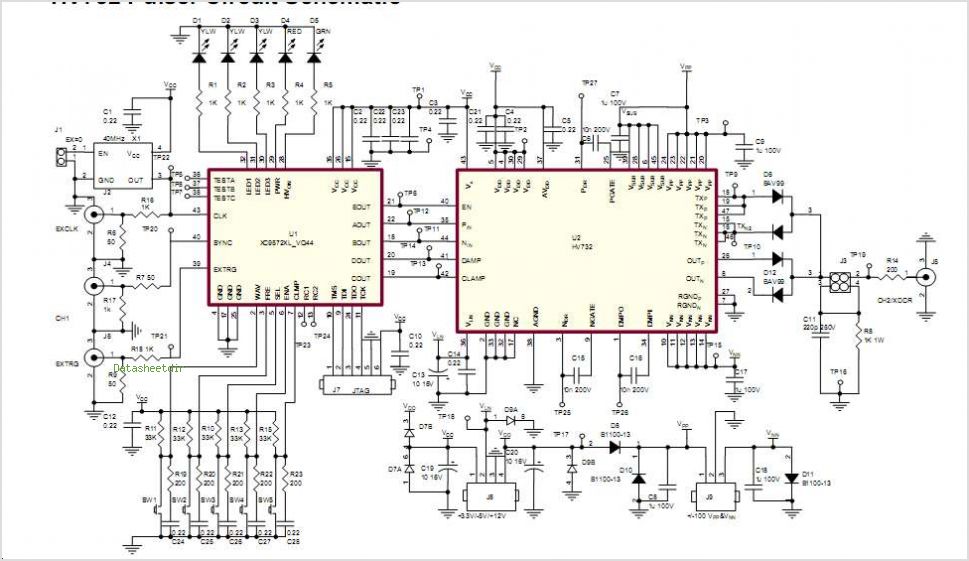

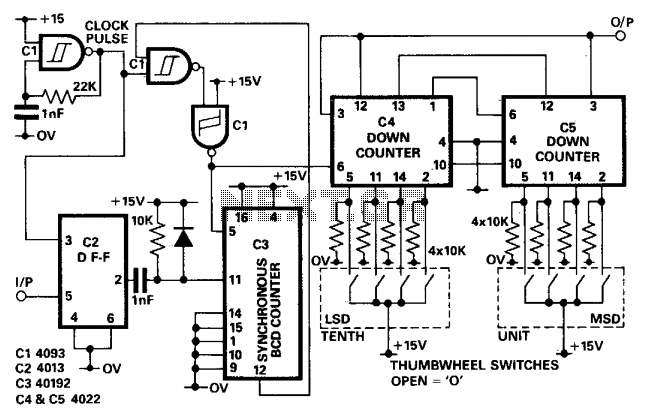

In applications where the period of the input pulses is uneven and a divider is required to accommodate a wide range of frequencies, a non-integer programmable pulse divider can be utilized. The D-type flip-flop (IC2) serves to synchronize the input signal with the clock pulse. When the clock pulse transitions from low to high and the input is high, the output of IC2 becomes high. Following this, IC3 resets to zero and initiates counting. The output pulse count from IC3 is ten times that of the input pulse. IC4 and IC5 are cascaded to create a two-decade programmable down counter.

The non-integer programmable pulse divider circuit is designed to effectively handle input signals with varying pulse periods, making it suitable for applications that require precise frequency division. The core component, the D-type flip-flop (IC2), plays a critical role in ensuring that the input signal is accurately synchronized with the clock signal, which is essential for reliable operation. The rising edge of the clock signal triggers IC2, which then outputs a high signal when the input is also high.

IC3, which functions as a counter, is reset to zero upon receiving the synchronized signal from IC2. It begins counting up from this reset state, allowing for the generation of an output pulse that is ten times the frequency of the input pulse. This amplification of the pulse count is vital for applications where increased output frequency is necessary.

Furthermore, to extend the counting capabilities, IC4 and IC5 are configured in a cascaded arrangement, forming a two-decade programmable down counter. This configuration allows for flexible programming of the output count, enabling the circuit to be tailored for specific frequency division requirements. The cascading of these counters enhances the overall functionality and versatility of the pulse divider, making it an essential component in various electronic applications where frequency manipulation is required.In applications where the period of the input pulses is uneven and the divider is required to cover a wide range of frequencies, the non-integer programmable pulse divider shown can be used. The purpose of the D-type flip-flop (IC2) is to synchronize the input signal with the clock pulse. When the clock pulse changes from low to high and the input is high, IC2 output goes high. Subsequently, IC3 resets to zero and starts counting up. The number of pulses at the output of IC3 is ten time the input pulse. IC4 and ICS are cascaded to form a two decade programmable down counter.

The non-integer programmable pulse divider circuit is designed to effectively handle input signals with varying pulse periods, making it suitable for applications that require precise frequency division. The core component, the D-type flip-flop (IC2), plays a critical role in ensuring that the input signal is accurately synchronized with the clock signal, which is essential for reliable operation. The rising edge of the clock signal triggers IC2, which then outputs a high signal when the input is also high.

IC3, which functions as a counter, is reset to zero upon receiving the synchronized signal from IC2. It begins counting up from this reset state, allowing for the generation of an output pulse that is ten times the frequency of the input pulse. This amplification of the pulse count is vital for applications where increased output frequency is necessary.

Furthermore, to extend the counting capabilities, IC4 and IC5 are configured in a cascaded arrangement, forming a two-decade programmable down counter. This configuration allows for flexible programming of the output count, enabling the circuit to be tailored for specific frequency division requirements. The cascading of these counters enhances the overall functionality and versatility of the pulse divider, making it an essential component in various electronic applications where frequency manipulation is required.In applications where the period of the input pulses is uneven and the divider is required to cover a wide range of frequencies, the non-integer programmable pulse divider shown can be used. The purpose of the D-type flip-flop (IC2) is to synchronize the input signal with the clock pulse. When the clock pulse changes from low to high and the input is high, IC2 output goes high. Subsequently, IC3 resets to zero and starts counting up. The number of pulses at the output of IC3 is ten time the input pulse. IC4 and ICS are cascaded to form a two decade programmable down counter.