Phase-Locked 20-Mhz Oscillator

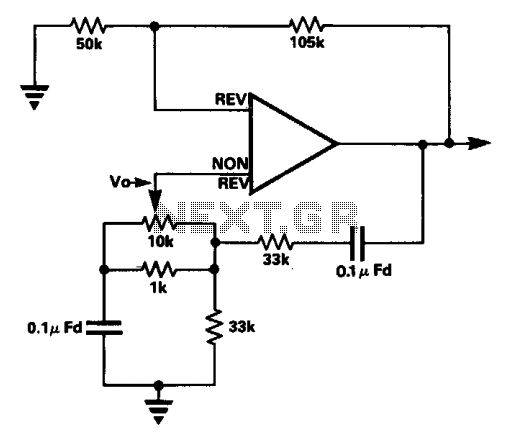

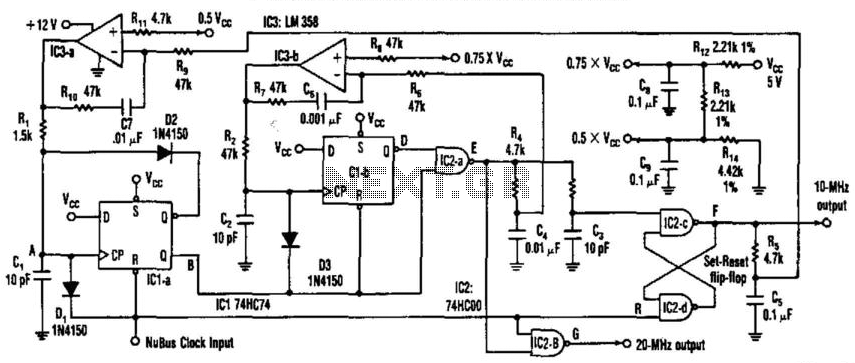

This circuit generates a 20-MHz clock signal that is phase locked to a 10-MHz clock found in the Apple MAC II. To create the 20-MHz output, the circuit generates a 25 ns negative-going pulse that is delayed by 50 ns from the falling edge of the 10-MHz Nubus clock input at point E. By performing a NOR operation on that pulse with the Nubus clock, the 20-MHz clock is produced at point G. Additionally, applying the 25 ns pulse to the set input of an S/R flip-flop and the Nubus clock to the reset input results in a 10-MHz square wave at point F.

The circuit operates by utilizing a phase-locked loop (PLL) methodology to ensure that the output clock signal maintains a consistent phase relationship with the reference clock. The 10-MHz Nubus clock serves as the reference signal, which is critical for synchronizing the subsequent clock generation.

The generation of the 25 ns negative-going pulse is achieved through a timing circuit that includes a delay line or a monostable multivibrator. This pulse is strategically delayed by 50 ns to align with the timing requirements of the circuit, ensuring that the output signal transitions occur at the correct intervals.

The NOR gate performs a logical operation where the output is high only when both inputs are low. By applying the delayed pulse and the Nubus clock to the inputs of the NOR gate, the resulting output at point G effectively toggles at 20 MHz, which is double the frequency of the input clock. This is due to the nature of the NOR operation combined with the timing of the inputs.

The S/R flip-flop is utilized to generate the 10-MHz square wave at point F. The set input is triggered by the 25 ns pulse, while the reset input is driven by the 10-MHz Nubus clock. This configuration allows the flip-flop to toggle its output state, producing a square wave that oscillates at half the frequency of the clock input, thus yielding the desired 10-MHz signal.

Overall, this circuit exemplifies a robust design for clock generation and synchronization, suitable for applications requiring precise timing signals, such as in digital electronics and microprocessor systems. This circuit produces a 20-MHz clock phase locked to a 10-MHz clock present in the Apple MAC II. To generate the 20-MHz signal, the circuit produces a 25 ns negative-going pulse delayed 50 ns from the falling edge of the 10-MHz Nubus clock input at point E. NORing that pulse with the Nubus clock produces the 20-MHz clock at point G. Applying the 25-ms pulse to the set input of an S/R flip-flop and the Nubus clock to the reset input results in a 10-MHz square wave at F.

🔗 External reference

The circuit operates by utilizing a phase-locked loop (PLL) methodology to ensure that the output clock signal maintains a consistent phase relationship with the reference clock. The 10-MHz Nubus clock serves as the reference signal, which is critical for synchronizing the subsequent clock generation.

The generation of the 25 ns negative-going pulse is achieved through a timing circuit that includes a delay line or a monostable multivibrator. This pulse is strategically delayed by 50 ns to align with the timing requirements of the circuit, ensuring that the output signal transitions occur at the correct intervals.

The NOR gate performs a logical operation where the output is high only when both inputs are low. By applying the delayed pulse and the Nubus clock to the inputs of the NOR gate, the resulting output at point G effectively toggles at 20 MHz, which is double the frequency of the input clock. This is due to the nature of the NOR operation combined with the timing of the inputs.

The S/R flip-flop is utilized to generate the 10-MHz square wave at point F. The set input is triggered by the 25 ns pulse, while the reset input is driven by the 10-MHz Nubus clock. This configuration allows the flip-flop to toggle its output state, producing a square wave that oscillates at half the frequency of the clock input, thus yielding the desired 10-MHz signal.

Overall, this circuit exemplifies a robust design for clock generation and synchronization, suitable for applications requiring precise timing signals, such as in digital electronics and microprocessor systems. This circuit produces a 20-MHz clock phase locked to a 10-MHz clock present in the Apple MAC II. To generate the 20-MHz signal, the circuit produces a 25 ns negative-going pulse delayed 50 ns from the falling edge of the 10-MHz Nubus clock input at point E. NORing that pulse with the Nubus clock produces the 20-MHz clock at point G. Applying the 25-ms pulse to the set input of an S/R flip-flop and the Nubus clock to the reset input results in a 10-MHz square wave at F.

🔗 External reference