Ramp generator

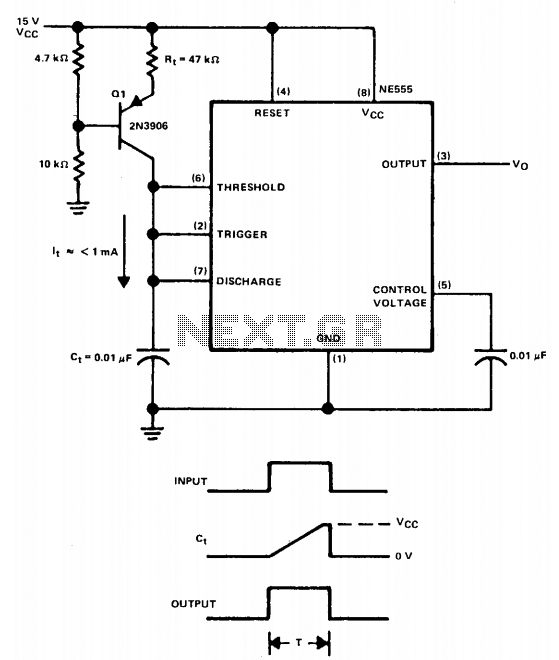

The linear charging ramp is particularly beneficial in applications requiring linear voltage control. Potential uses include long-duration voltage-controlled timers, voltage-to-pulse width converters, and linear pulse width modulators. Q1 acts as the current source transistor, providing a constant current to the timing capacitor Ct. Upon triggering the timer, the clamp on Ct is released, allowing Ct to charge linearly towards Vcc due to the constant current supplied by Q1. The threshold at pin 6 is defined as approximately 3 Vcc, referred to as Vc. When the voltage across Ct reaches Vc volts, the timing cycle concludes. The timing expression for the output pulse width is as follows:

The linear charging ramp circuit is essential for applications that necessitate precise voltage control over time. The architecture typically consists of a current source transistor, Q1, which is responsible for supplying a steady current to a timing capacitor, Ct. This configuration allows for the capacitor to charge in a linear manner when the timer is activated.

Upon activation, the clamp mechanism on the capacitor is disengaged, permitting Ct to charge towards the supply voltage (Vcc). The linear ramping of the voltage across Ct is dictated by the constant current provided by Q1, ensuring that the charge time is predictable and can be finely controlled.

The operational threshold for the timer is set at approximately three times the supply voltage (3 Vcc), noted as Vc. When the voltage across the timing capacitor reaches this threshold, the timing cycle is terminated, resulting in a pulse output. The output pulse width can be calculated using a specific timing expression, which is dependent on the values of the components in the circuit, including the capacitance of Ct and the current supplied by Q1.

This configuration is particularly advantageous in applications such as timers, where a precise timing interval is critical, as well as in pulse width modulation scenarios where control over the duty cycle is necessary. By adjusting the current through Q1 or the capacitance of Ct, the timing characteristics can be tailored to meet the specific requirements of the application.The linear charging ramp is most useful where linear control of voltage is required. Some possible applications are a long period voltage controlled timer, a voltage to pulse width converter, or a linear pulse width modulator. Ql is the current source transistor, supplying constant current to the timing capacitor Ct. When the timer is triggered, the clamp on Ct is removed and Ct charges linearly toward Vcc by virtue of the constant current supplied by Ql.

The threshold at pin 6 is ¥3 Vcc; here, it is termed Vc. When the voltage across Ct reaches Vc volts, the timing cycle ends. The timing expression for output pulse with is:

The linear charging ramp circuit is essential for applications that necessitate precise voltage control over time. The architecture typically consists of a current source transistor, Q1, which is responsible for supplying a steady current to a timing capacitor, Ct. This configuration allows for the capacitor to charge in a linear manner when the timer is activated.

Upon activation, the clamp mechanism on the capacitor is disengaged, permitting Ct to charge towards the supply voltage (Vcc). The linear ramping of the voltage across Ct is dictated by the constant current provided by Q1, ensuring that the charge time is predictable and can be finely controlled.

The operational threshold for the timer is set at approximately three times the supply voltage (3 Vcc), noted as Vc. When the voltage across the timing capacitor reaches this threshold, the timing cycle is terminated, resulting in a pulse output. The output pulse width can be calculated using a specific timing expression, which is dependent on the values of the components in the circuit, including the capacitance of Ct and the current supplied by Q1.

This configuration is particularly advantageous in applications such as timers, where a precise timing interval is critical, as well as in pulse width modulation scenarios where control over the duty cycle is necessary. By adjusting the current through Q1 or the capacitance of Ct, the timing characteristics can be tailored to meet the specific requirements of the application.The linear charging ramp is most useful where linear control of voltage is required. Some possible applications are a long period voltage controlled timer, a voltage to pulse width converter, or a linear pulse width modulator. Ql is the current source transistor, supplying constant current to the timing capacitor Ct. When the timer is triggered, the clamp on Ct is removed and Ct charges linearly toward Vcc by virtue of the constant current supplied by Ql.

The threshold at pin 6 is ¥3 Vcc; here, it is termed Vc. When the voltage across Ct reaches Vc volts, the timing cycle ends. The timing expression for output pulse with is: