Sample and hold circuit II

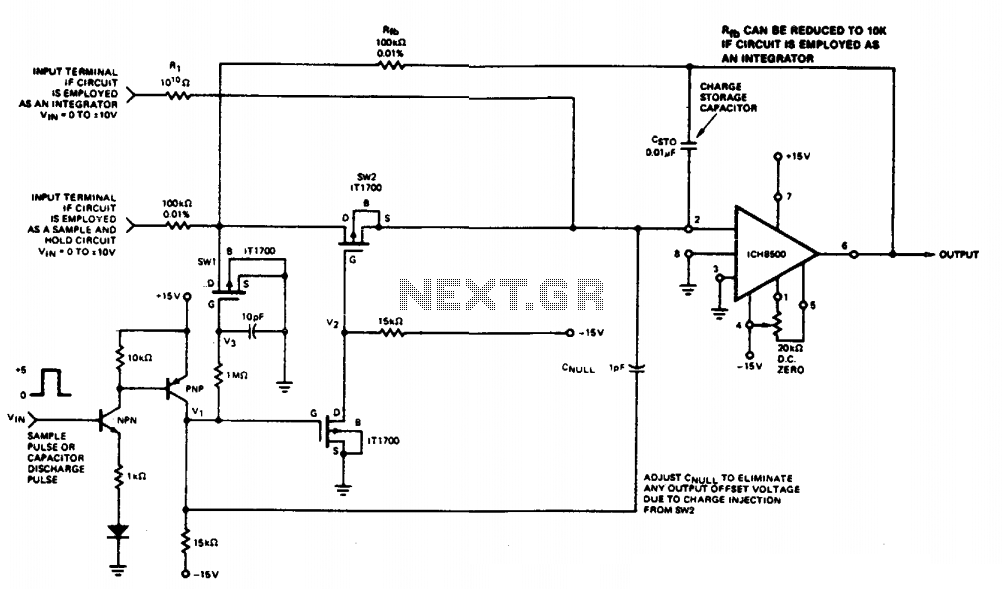

This circuit quickly charges capacitor CST0 to a voltage that matches an input signal. After charging, the input signal is electrically disconnected from the capacitor, allowing the charge to remain on CST0. Since CST0 is part of the negative feedback loop of the operational amplifier, the amplifier's output voltage corresponds to the voltage across the capacitor. Ideally, the voltage across CST0 should remain stable, which would keep the amplifier's output constant. However, the voltage across CST0 will decrease at a rate that is proportional to the current being added or removed from the current summing node of the amplifier. This current can arise from four sources: the leakage resistance of CST0, leakage current from the solid-state switch SW2, currents through high-resistance paths in the circuit fixture, and most importantly, the bias current of the operational amplifier. When using the ICH8500A operational amplifier, this bias current is nearly negligible (less than 0.01 µA). It is important to note that the voltages at the source, drain, and gate of switch SW2 are zero or nearly zero when the circuit is in hold mode. Careful construction can minimize stray resistance paths, and capacitor resistance can be significantly reduced with the selection of a high-quality capacitor. The end result is a low-drift sample-and-hold circuit. Furthermore, the circuit can also function as an integrator, where the input voltage is applied to the integrator input terminal. The time constant of the circuit is determined by the product of Rl and Cg.

The described circuit primarily functions as a sample-and-hold circuit, utilizing an operational amplifier in a negative feedback configuration. The capacitor CST0 plays a crucial role in maintaining the voltage level that corresponds to the input signal, ensuring that the output of the amplifier remains stable during the hold phase. The operational amplifier, specifically the ICH8500A, is chosen for its minimal bias current, which is essential for maintaining low drift in the output voltage.

In the hold mode, the solid-state switch SW2 disconnects the input signal, allowing the charge on CST0 to be preserved. The design accounts for various leakage paths that could affect the performance, including the inherent leakage resistance of the capacitor itself and any parasitic resistances in the circuit layout. To mitigate these effects, careful PCB design practices should be employed, including short trace lengths and the use of high-quality components.

When utilized as an integrator, the circuit can integrate the input voltage over time, with the output reflecting the accumulated value. The time constant, dictated by the resistor Rl and capacitor Cg, is a critical parameter that determines the response time and stability of the integration process. This versatility makes the circuit suitable for a range of applications, including analog signal processing and data acquisition systems, where accurate voltage representation and stability are paramount.

Overall, the design emphasizes low drift and high accuracy, making it ideal for precision applications in electronic instrumentation and control systems.This circuit rapidly charges capacitor CST0 to a voltage equal to an input signal. The input signal is then electrically disconnected from the capacitor with the charge still remaining on CSTO. Since CST0 is in the negative feedback loop of the operational amplifier, the output voltage of the amplifier is equal to the voltage across the capacitor.

Ideally, the voltage across CST0 should remain constant causing the output of the amplifier to remain constant as well. However, the voltage across CST0 will decay at a rate proportional to the current being injected or taken out of the current summing node of the amplifier.

This current can come from four sources: leakage resistance of CST0, leakage current due to the solid state switch SW2, currents due to high resistance paths on the circuit fixture, and most important, bias current of the operational amplifier. If the ICH8500A operational amplifier is employed, this bids current is almost non-existent (less than O.OlpA).

Note that the voltages on the source, drain and gate of switch SW2 are zero or near zero when the circuit is in the hold mode. Careful construction will eliminate stray resistance paths and capacitor resistance can be eliminated if a quality capacitor is selected.

The net result is a low drift sample and hold circuit. The circuit can double as an integrator. In this application the input voltage is applied to the integrator input terminal. The time constant of the circuit is the product of Rl and Cg🔗 External reference

The described circuit primarily functions as a sample-and-hold circuit, utilizing an operational amplifier in a negative feedback configuration. The capacitor CST0 plays a crucial role in maintaining the voltage level that corresponds to the input signal, ensuring that the output of the amplifier remains stable during the hold phase. The operational amplifier, specifically the ICH8500A, is chosen for its minimal bias current, which is essential for maintaining low drift in the output voltage.

In the hold mode, the solid-state switch SW2 disconnects the input signal, allowing the charge on CST0 to be preserved. The design accounts for various leakage paths that could affect the performance, including the inherent leakage resistance of the capacitor itself and any parasitic resistances in the circuit layout. To mitigate these effects, careful PCB design practices should be employed, including short trace lengths and the use of high-quality components.

When utilized as an integrator, the circuit can integrate the input voltage over time, with the output reflecting the accumulated value. The time constant, dictated by the resistor Rl and capacitor Cg, is a critical parameter that determines the response time and stability of the integration process. This versatility makes the circuit suitable for a range of applications, including analog signal processing and data acquisition systems, where accurate voltage representation and stability are paramount.

Overall, the design emphasizes low drift and high accuracy, making it ideal for precision applications in electronic instrumentation and control systems.This circuit rapidly charges capacitor CST0 to a voltage equal to an input signal. The input signal is then electrically disconnected from the capacitor with the charge still remaining on CSTO. Since CST0 is in the negative feedback loop of the operational amplifier, the output voltage of the amplifier is equal to the voltage across the capacitor.

Ideally, the voltage across CST0 should remain constant causing the output of the amplifier to remain constant as well. However, the voltage across CST0 will decay at a rate proportional to the current being injected or taken out of the current summing node of the amplifier.

This current can come from four sources: leakage resistance of CST0, leakage current due to the solid state switch SW2, currents due to high resistance paths on the circuit fixture, and most important, bias current of the operational amplifier. If the ICH8500A operational amplifier is employed, this bids current is almost non-existent (less than O.OlpA).

Note that the voltages on the source, drain and gate of switch SW2 are zero or near zero when the circuit is in the hold mode. Careful construction will eliminate stray resistance paths and capacitor resistance can be eliminated if a quality capacitor is selected.

The net result is a low drift sample and hold circuit. The circuit can double as an integrator. In this application the input voltage is applied to the integrator input terminal. The time constant of the circuit is the product of Rl and Cg