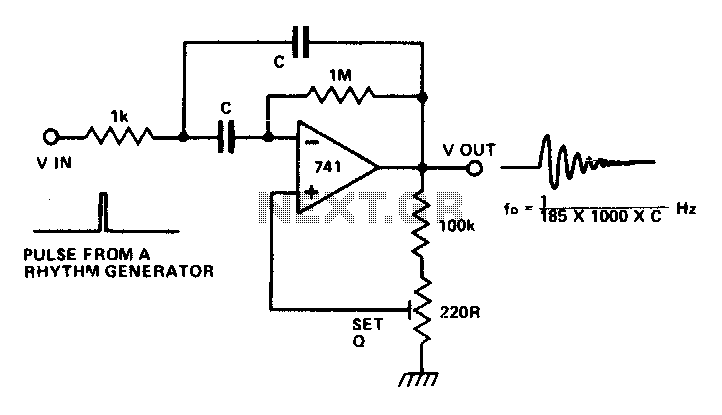

Simple sine-wave generator has no low- or high-pass filters

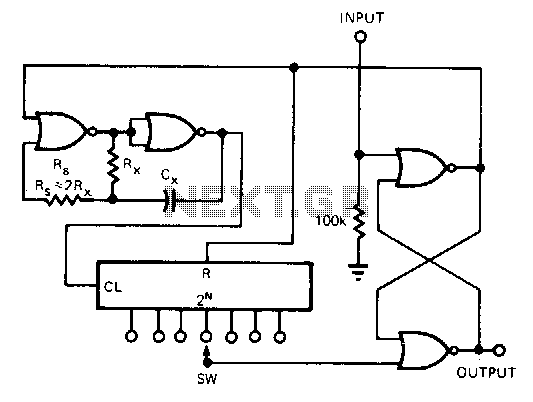

Generating sine waves with controlled frequencies over a wide range is challenging when using RC or LC sinusoidal oscillators. However, this can be effectively achieved using a wideband digital square wave oscillator, a counter, and a weighted summing network. The circuit can produce a sinusoidal output signal with a frequency range of 100,000,000+:1, spanning from approximately 1 MHz to under 0.01 Hz, without the need for any low-pass or high-pass filters. The circuit consists of two main components. The first component is a counter IC with a controlled inverter (IC2) that sequences the switching of input resistors in the second component, which is a summing amplifier (IC3). EXOR gates are utilized to invert signals from four outputs (Q0-Q3) of the IC1 counter, based on the logical value of the fifth output (Q4). This process generates the positive and negative halves of the sine waveform. Each half is divided into 16 parts. The logical values from IC1's outputs (Q0-Q4) produce weighted symmetrical currents at the summing junction of IC3. The amplifier combines all four weighted currents to generate an output signal with the desired sinusoidal waveform. Each output signal period requires 32 periods of the input signal, meaning the input clock frequency must be 32 times greater than the desired frequency of the output analog signal.

The circuit architecture consists of a digital square wave oscillator that acts as the frequency source, producing a high-frequency square wave signal. The counter IC (IC1) divides this input frequency, generating a series of binary outputs (Q0-Q4). The outputs Q0 to Q3 provide the necessary signals for creating the sine wave's alternating halves, while Q4 serves as a control signal for the EXOR gates, ensuring proper signal inversion.

The inverter (IC2) is crucial for sequencing the input resistors connected to the summing amplifier (IC3). By controlling which resistors are active at any given time, the circuit shapes the waveform. The summing amplifier integrates the weighted contributions from the resistors, where each resistor corresponds to a specific part of the sine wave. The weighted currents at the summing junction are critical; they must be carefully calculated to ensure that the resulting waveform accurately represents a sine wave.

The EXOR gates play a pivotal role in determining the output waveform's phase by inverting the signals based on the control logic provided by Q4. This logic ensures that the output waveform alternates correctly between positive and negative halves, maintaining the integrity of the sine wave shape.

For optimal performance, the circuit requires that the input clock frequency be maintained at 32 times the desired output frequency. This high clock rate allows for a smooth approximation of the sine wave, as the summing amplifier effectively integrates the contributions from each of the 16 segments of the waveform.

Overall, this circuit design provides a versatile solution for generating high-quality sine waves across a broad frequency spectrum, suitable for various applications in signal processing and waveform generation.Generating sine waves with controlled frequencies over a wide range is difficult when using RC or LC sinusoidal oscillators. However, this performance can be simply created using a wideband digital squarewave oscillator, a counter, and a weighted summing network.

Using the circuit shown, a sinusoidal output signal with a 100, 000, 000+:1 frequency range from about 1 MHz to under 0. 01 Hz can be obtained without need for any lowpass or high-pass filters. The circuit consists of two parts. The first part is a counter IC with a controlled inverter (IC2) that sequences the switching of input resistors of the second part ”a summing amplifier (IC3). The EXOR gates are used to invert signals from four of IC1 counter`s outputs (Q0-Q3), depending on logical value at the fifth counter output (Q4).

This operation creates the positive and negative halves of the sine waveform. Each of these halves consists of 24 = 16 parts. The logical values at IC1`s Q0-Q4 outputs produce weightedsymmetrical currents at the summing junction of IC3. The amplifier adds all four weighted currents and generates an output signal with the desired sinusoidal waveform.

Every period of the output signal needs 16 * 2 = 32 periods of input signal, i. e. the frequency of input clock signal must be 32 times higher than the desired frequency of output analog signal: 🔗 External reference

The circuit architecture consists of a digital square wave oscillator that acts as the frequency source, producing a high-frequency square wave signal. The counter IC (IC1) divides this input frequency, generating a series of binary outputs (Q0-Q4). The outputs Q0 to Q3 provide the necessary signals for creating the sine wave's alternating halves, while Q4 serves as a control signal for the EXOR gates, ensuring proper signal inversion.

The inverter (IC2) is crucial for sequencing the input resistors connected to the summing amplifier (IC3). By controlling which resistors are active at any given time, the circuit shapes the waveform. The summing amplifier integrates the weighted contributions from the resistors, where each resistor corresponds to a specific part of the sine wave. The weighted currents at the summing junction are critical; they must be carefully calculated to ensure that the resulting waveform accurately represents a sine wave.

The EXOR gates play a pivotal role in determining the output waveform's phase by inverting the signals based on the control logic provided by Q4. This logic ensures that the output waveform alternates correctly between positive and negative halves, maintaining the integrity of the sine wave shape.

For optimal performance, the circuit requires that the input clock frequency be maintained at 32 times the desired output frequency. This high clock rate allows for a smooth approximation of the sine wave, as the summing amplifier effectively integrates the contributions from each of the 16 segments of the waveform.

Overall, this circuit design provides a versatile solution for generating high-quality sine waves across a broad frequency spectrum, suitable for various applications in signal processing and waveform generation.Generating sine waves with controlled frequencies over a wide range is difficult when using RC or LC sinusoidal oscillators. However, this performance can be simply created using a wideband digital squarewave oscillator, a counter, and a weighted summing network.

Using the circuit shown, a sinusoidal output signal with a 100, 000, 000+:1 frequency range from about 1 MHz to under 0. 01 Hz can be obtained without need for any lowpass or high-pass filters. The circuit consists of two parts. The first part is a counter IC with a controlled inverter (IC2) that sequences the switching of input resistors of the second part ”a summing amplifier (IC3). The EXOR gates are used to invert signals from four of IC1 counter`s outputs (Q0-Q3), depending on logical value at the fifth counter output (Q4).

This operation creates the positive and negative halves of the sine waveform. Each of these halves consists of 24 = 16 parts. The logical values at IC1`s Q0-Q4 outputs produce weightedsymmetrical currents at the summing junction of IC3. The amplifier adds all four weighted currents and generates an output signal with the desired sinusoidal waveform.

Every period of the output signal needs 16 * 2 = 32 periods of input signal, i. e. the frequency of input clock signal must be 32 times higher than the desired frequency of output analog signal: 🔗 External reference