Symmetric Noise Source

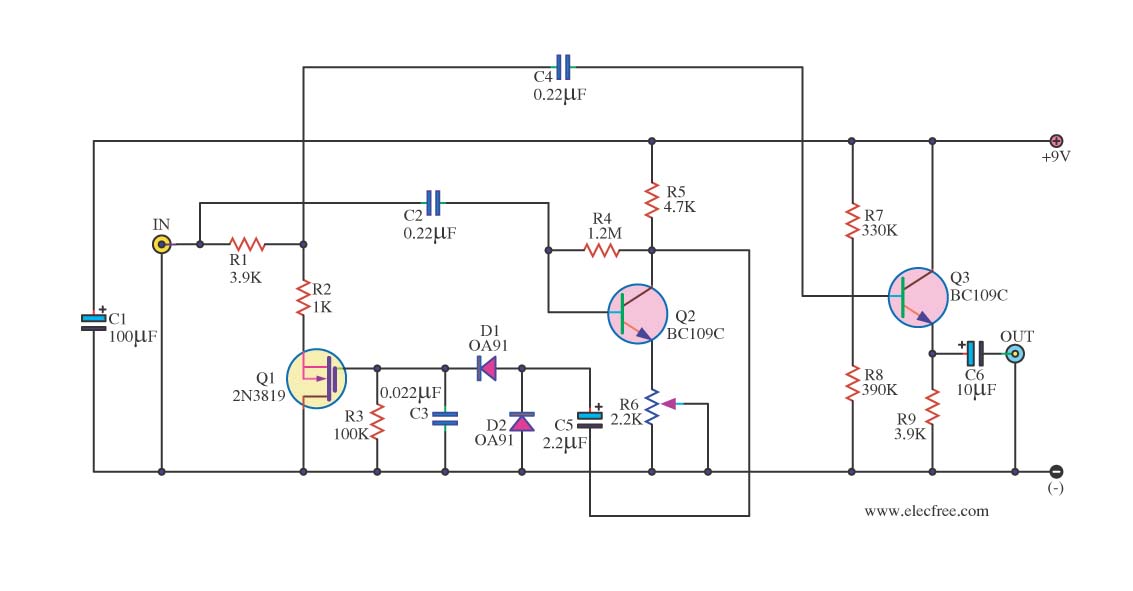

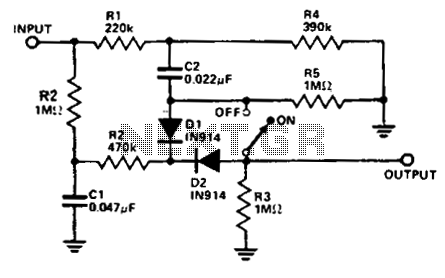

When a transistor junction operates in Zener breakdown as a noise source, the resulting noise signal exhibits asymmetry in amplitude. This issue can be addressed by employing two transistors as independent noise sources. One transistor is connected with a series resistor to ground, while the other is connected with a series resistor to the supply line. Each transistor generates an asymmetric noise voltage, but with opposite asymmetries. When these two voltages are combined, the resultant amplitude becomes symmetric. In the schematic, T1 and T2 represent the noise sources, with R2 serving as the series resistor to ground and R4 as the series resistor to the positive supply line. The supply voltage for the noise sources is adjustable, allowing for the optimization of the transistors' noise generation, as the noise produced is dependent on the power supply voltage. P1 and R1 provide an adjustable supply voltage ranging from 8 to 12 V for T1, while P3 and R3 serve the same purpose for T2. Capacitors C3 and C5 are used to smooth these voltages. Given that the amplitudes of the two noise sources will not match, a weighted sum of the two signals is necessary. To facilitate this, P2 is included between the outputs of the noise sources, acting as a balance control. Additionally, since the DC levels of the two noise sources differ, C4 is incorporated into the balance network. The weighted sum of the two signals appears at the wiper of P2, superimposed on the DC signal from noise source T1. This DC level also provides the necessary bias for the buffer stage T3, which isolates the noise sources from any connected output circuit. For circuit adjustment, an oscilloscope should be connected to the output. Initially, P2 should be turned fully to the left, and P1 adjusted until the maximum noise signal is observed on the oscilloscope. Subsequently, P2 should be turned fully to the right, followed by adjusting P3 for optimal noise signal. Finally, P3 should be adjusted to achieve a symmetric noise signal. The circuit is designed to provide an output voltage of approximately 150 mV peak-to-peak, with a current consumption of 2 mA. The oscilloscope displays the asymmetric noise signal on channel 2 and the symmetric noise signal on channel 1.

The described circuit effectively utilizes two transistors operating in Zener breakdown mode to generate noise signals that compensate for each other's asymmetries. By strategically placing resistors and capacitors, the circuit not only optimizes the noise generation but also ensures that the output signal is balanced and symmetric. The adjustable voltage supply allows for fine-tuning of the noise characteristics, which is vital for applications requiring precise noise levels. The inclusion of a buffer stage is crucial, as it prevents loading effects that could distort the noise signals when interfacing with subsequent circuitry. The use of an oscilloscope for real-time adjustments enhances the accuracy of the setup, allowing for immediate visual feedback on the noise characteristics. This design is particularly useful in applications such as testing, signal processing, and noise analysis, where controlled noise generation is essential. The careful selection of component values and configurations ensures reliable operation and optimal performance of the noise generator circuit.If a transistor junction operating in Zener breakdown is used as a noise source, the amplitude of the noise signal is asymmetric. This problem can be solved by using two transistors as two independent noise sources. One of these has a series resistor to earth, and the other has a series resistor to the supply line. Each of these noise sources prod uces an asymmetric noise voltage, with opposite asymmetry. If these two voltages are combined, the amplitude of the result will be symmetric. In the circuit diagram, T1 and T2 are the noise sources. The series resistors are R2 (to earth) and R4 (to the positive supply line). The supply voltage for the noise sources has been made adjustable, to allow the noise generation of the transistors to be optimized. This is because the amount of noise produced depends on the power supply voltage. P1 and R1 provide an adjustable supply voltage between 8 and 12 V for the noise stage around T1, while P3 and R3 perform the same function for T2.

C3 and C5 smooth these voltages. Since the amplitudes of the two noise sources will never be the same, it is necessary to take a weighted sum of the two signals. Consequently, P2 is included between the outputs of the noise sources as a sort of balance control. Since the DC levels of the two noise sources are not the same, C4 is also included in the balance network.

The weighted sum of the two signals is present on the wiper of P2, superimposed on the DC signal of noise source T1. This DC level is also used for the DC bias of the buffer stage T3. The buffer isolates the noise sources from whatever circuit is connected to the output. To adjust the circuit, connect an oscilloscope to the output. First, turn P2 all the way to the left. Now rotate P1 until a maximum noise signal is seen on the oscilloscope. Next, turn P2 all the way to the right, and then adjust P3 for the best noise signal. Finally, adjust P3 so that the noise signal looks symmetric. The circuit provides an output voltage of approximately 150mV pp. The current consumption is 2mA. The oscilloscope shows the asymmetric noise signal on channel 2, and the symmetric noise signal on channel 1.

🔗 External reference

The described circuit effectively utilizes two transistors operating in Zener breakdown mode to generate noise signals that compensate for each other's asymmetries. By strategically placing resistors and capacitors, the circuit not only optimizes the noise generation but also ensures that the output signal is balanced and symmetric. The adjustable voltage supply allows for fine-tuning of the noise characteristics, which is vital for applications requiring precise noise levels. The inclusion of a buffer stage is crucial, as it prevents loading effects that could distort the noise signals when interfacing with subsequent circuitry. The use of an oscilloscope for real-time adjustments enhances the accuracy of the setup, allowing for immediate visual feedback on the noise characteristics. This design is particularly useful in applications such as testing, signal processing, and noise analysis, where controlled noise generation is essential. The careful selection of component values and configurations ensures reliable operation and optimal performance of the noise generator circuit.If a transistor junction operating in Zener breakdown is used as a noise source, the amplitude of the noise signal is asymmetric. This problem can be solved by using two transistors as two independent noise sources. One of these has a series resistor to earth, and the other has a series resistor to the supply line. Each of these noise sources prod uces an asymmetric noise voltage, with opposite asymmetry. If these two voltages are combined, the amplitude of the result will be symmetric. In the circuit diagram, T1 and T2 are the noise sources. The series resistors are R2 (to earth) and R4 (to the positive supply line). The supply voltage for the noise sources has been made adjustable, to allow the noise generation of the transistors to be optimized. This is because the amount of noise produced depends on the power supply voltage. P1 and R1 provide an adjustable supply voltage between 8 and 12 V for the noise stage around T1, while P3 and R3 perform the same function for T2.

C3 and C5 smooth these voltages. Since the amplitudes of the two noise sources will never be the same, it is necessary to take a weighted sum of the two signals. Consequently, P2 is included between the outputs of the noise sources as a sort of balance control. Since the DC levels of the two noise sources are not the same, C4 is also included in the balance network.

The weighted sum of the two signals is present on the wiper of P2, superimposed on the DC signal of noise source T1. This DC level is also used for the DC bias of the buffer stage T3. The buffer isolates the noise sources from whatever circuit is connected to the output. To adjust the circuit, connect an oscilloscope to the output. First, turn P2 all the way to the left. Now rotate P1 until a maximum noise signal is seen on the oscilloscope. Next, turn P2 all the way to the right, and then adjust P3 for the best noise signal. Finally, adjust P3 so that the noise signal looks symmetric. The circuit provides an output voltage of approximately 150mV pp. The current consumption is 2mA. The oscilloscope shows the asymmetric noise signal on channel 2, and the symmetric noise signal on channel 1.

🔗 External reference