telephone ring generator circuit

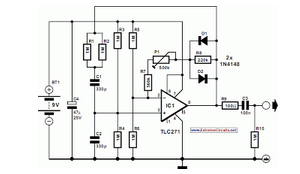

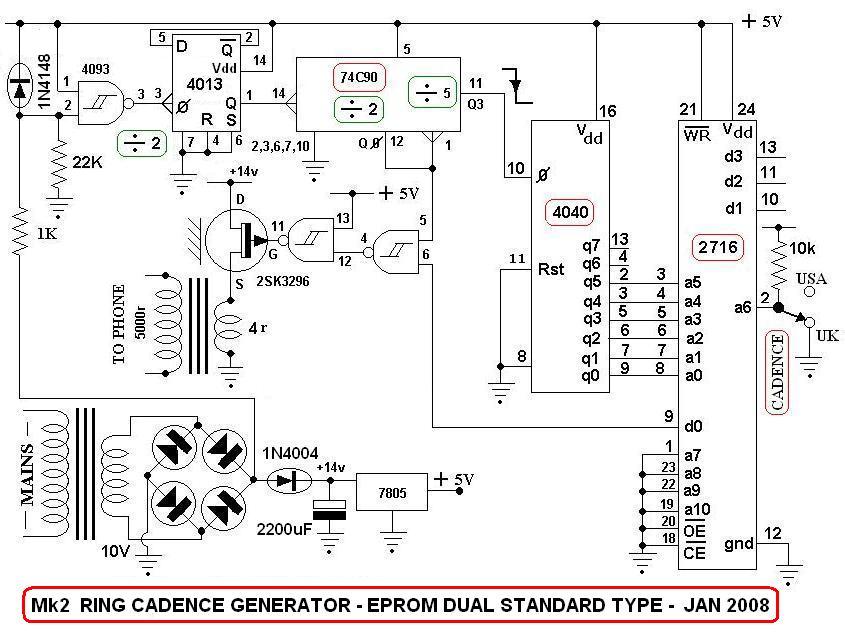

This is a switch-selectable dual output version of a previous design from 2007, utilizing a field-programmed EPROM to generate two versions of the ringing sequence. The AC mains voltage is stepped down to approximately 10 V AC and then directed to a bridge rectifier, filter capacitor, and a three-terminal voltage regulator. A series diode is placed between the positive terminal of the bridge rectifier and the filter capacitor. At the anode of this diode, a pulsating 100 Hz unidirectional sinusoid is produced, which serves as an accurate clock signal (the cathode end provides filtered DC voltage). This positive-going sinusoid is supplied to a 4093 Schmitt trigger, which generates a fast rise and fall square wave output necessary for clocking subsequent logic ICs. A clamping diode between the Schmitt input (pin 2) and the Vcc rail prevents the input from exceeding one diode drop above Vcc, with excess voltage being dropped across a 1K resistor. Experimental results indicated that a 22K bleed resistor was required at the gate input to avoid lock-up due to charge storage effects. The cleaned-up 100 Hz clock signal is then fed to a 4013 D-type flip-flop, which divides the signal by 2, yielding a 50 Hz mark/space signal. This output is then fed to a 7490 counter, which further divides the signal by 2 to produce a 25 Hz ringing frequency, and by 5 to achieve a 5 Hz or 200 ms interval suitable for generating the correct ring cadence. The sequential outputs of a 4040 counter are connected to the address lines of a 2716 EPROM, which has been field-programmed to provide a serial output bit-stream at a 200 ms interval, serving as a gating signal to enable and disable the 25 Hz ringing signal. For each 200 ms clock pulse, the EPROM output advances to the next sequential address. The first 64 locations contain the coding for two runs of the UK ringing sequence, while the subsequent 64 addresses encode the 4-second ring and 8-second silence US sequence. The design allows for flexibility, as many other types of sequences could be utilized, although only 128 address locations and one bit of the 8-bit wide data byte stored in the EPROM (D0) are employed. The EPROM contents are organized such that the highlighted locations indicate a "ring" signal, while all others represent silence. Gating is accomplished in the 4093 NAND gate, and its output directly drives a VMOS FET gate, which switches the unregulated 15 V rail onto the transformer primary. The VMOS FET is preferred over bipolar transistors due to its high power handling capacity and low on-state resistance (in milliohms), allowing most of the +15 V DC rail to be available to the transformer winding. These devices also feature an internal reverse-biased diode between the drain and source, providing protection against failure from transient spikes. The specified FET, 2SK3296, was salvaged from defunct P4 computer motherboards but suitable replacements are readily available. A 5000-ohm to 4-ohm loudspeaker transformer is utilized in reverse to step up the voltage to a level sufficient to actuate the bell solenoid armature (with a 1:35 ratio). The internal components (circuit board, fan, etc.) can be removed from a metal enclosure measuring 6" x 6" x 3", which is equipped with an IEC entry connector and an on/off mains switch, making it ready for reuse.

The circuit operates by first converting the AC mains to a lower voltage using a transformer, followed by rectification and filtration to obtain a stable DC supply. The clock generation circuitry, utilizing a Schmitt trigger and flip-flops, ensures a reliable timing signal for the EPROM, which holds the ringing sequences. The gating mechanism controlled by the NAND gate and VMOS FET allows for efficient switching of the ringing signal, ensuring minimal power loss and enhancing performance. The choice of components, such as the VMOS FET for its low on-resistance and built-in protection, reflects a design focused on reliability and efficiency. The system's modularity allows for various ringing sequences to be programmed into the EPROM, making it adaptable for different applications. The use of salvaged components not only reduces costs but also promotes sustainability in electronic design. This circuit exemplifies a practical approach to creating a customizable ringing device with modern electronic components and techniques.This is a switch selectable dual output "re-hashed" version of my previous (2007) design, and uses a field programmed EPROM for generating both versions of the ringing sequence. AC mains is stepped down to about 10 v AC and fed to the familiar bridge rectifier, filter capacitor and 3 terminal voltage regulator.

However a series diode is inserted b etween the + terminal of the bridge rectifier and the filter capacitor. Therefore at the anode end of this diode will be a pulsating 100Hz unidirectional sinusoid which is used as an accurate "clock" (Cathode end being filtered DC voltage) This positive going sinusoid is fed to a 4093 Schmitt trigger, its action produces a fast rise (and fall) square wave output necessary to clock following logic IC`s. A clamping diode b/w the Schmitt input (pin 2) and the Vcc rail precludes the input from rising greater than one diode drop above Vcc, excess voltage being dropped across 1K resistor.

It was found by experiment that a 22K "bleed" resistor was needed at the gate input to prevent "lock-up" due to some sort of "charge storage" effect. This cleaned-up 100Hz "clock" signal is now fed to a 4013 D type flip-flop which divides the signal by 2 and also gives a 50 Hz equi` mark/space signal.

This then feeds the 7490 where another divide by 2 gives; 25Hz (for ringing frequency) and further divide by 5 give 5Hz or a 200mS interval suitable for producing the correct ring cadence. The sequential outputs of the 4040 are connected to the address lines of a 2716 eprom which has been field programmed to provide a serial output bit-stream of 200mS interval used as a gating signal to enable on and off the 25Hz ringing signal.

For each 200mS clock pulse the output of the eprom moves to the next sequential address. The first 64 locations contain the necessary coding for two runs of the UK sequence and the next 64 memory addresses`s contain coding for the 4 sec ring, 8 sec silence US sequence. However the astute reader will realise that many other types would work, and in fact we are only using 128 address locations and one bit of the 8 bit wide data byte stored in the eprom (D0) The eprom contents are shown in the table (below) it can be seen that the pink higlighted locations represent a "ring" and all others silence (read from top to bottom) Gating is achieved in the 4093 NAND gate, its output then inverted directly feeds a VMOS FET gate which switches the unregulated 15v rail onto the transformer primary.

The VMOS FET is preferred over a bipolar transistor etc here because of their power handling capacity and very low "on" state resistance (milliohms) which allows most of the +15v DC rail be available to the transformer winding. Fortunately these devices also have an internal reversed biased diode, b/w drain and source which protects them against failure from transient spikes (refer to manuf` data sheets).

The particular FET specified 2SK3296, I salvaged several from defunct P4 computer mother board (in power supply circuit). However suitable replacement types are easily available. I have used a 5000 ohm to 4 ohm loud-speaker transformer (in reverse - so to speak) to step up the voltage to the level necessary the make the bell solenoid actuate the armature (1 : 35 ratio) Simply remove the internals (circuit board, fan etc) and you have a 6" x 6" x 3" sized metal box with IEC entry connector and on/off mains switch etc - ready for re-use.

🔗 External reference

The circuit operates by first converting the AC mains to a lower voltage using a transformer, followed by rectification and filtration to obtain a stable DC supply. The clock generation circuitry, utilizing a Schmitt trigger and flip-flops, ensures a reliable timing signal for the EPROM, which holds the ringing sequences. The gating mechanism controlled by the NAND gate and VMOS FET allows for efficient switching of the ringing signal, ensuring minimal power loss and enhancing performance. The choice of components, such as the VMOS FET for its low on-resistance and built-in protection, reflects a design focused on reliability and efficiency. The system's modularity allows for various ringing sequences to be programmed into the EPROM, making it adaptable for different applications. The use of salvaged components not only reduces costs but also promotes sustainability in electronic design. This circuit exemplifies a practical approach to creating a customizable ringing device with modern electronic components and techniques.This is a switch selectable dual output "re-hashed" version of my previous (2007) design, and uses a field programmed EPROM for generating both versions of the ringing sequence. AC mains is stepped down to about 10 v AC and fed to the familiar bridge rectifier, filter capacitor and 3 terminal voltage regulator.

However a series diode is inserted b etween the + terminal of the bridge rectifier and the filter capacitor. Therefore at the anode end of this diode will be a pulsating 100Hz unidirectional sinusoid which is used as an accurate "clock" (Cathode end being filtered DC voltage) This positive going sinusoid is fed to a 4093 Schmitt trigger, its action produces a fast rise (and fall) square wave output necessary to clock following logic IC`s. A clamping diode b/w the Schmitt input (pin 2) and the Vcc rail precludes the input from rising greater than one diode drop above Vcc, excess voltage being dropped across 1K resistor.

It was found by experiment that a 22K "bleed" resistor was needed at the gate input to prevent "lock-up" due to some sort of "charge storage" effect. This cleaned-up 100Hz "clock" signal is now fed to a 4013 D type flip-flop which divides the signal by 2 and also gives a 50 Hz equi` mark/space signal.

This then feeds the 7490 where another divide by 2 gives; 25Hz (for ringing frequency) and further divide by 5 give 5Hz or a 200mS interval suitable for producing the correct ring cadence. The sequential outputs of the 4040 are connected to the address lines of a 2716 eprom which has been field programmed to provide a serial output bit-stream of 200mS interval used as a gating signal to enable on and off the 25Hz ringing signal.

For each 200mS clock pulse the output of the eprom moves to the next sequential address. The first 64 locations contain the necessary coding for two runs of the UK sequence and the next 64 memory addresses`s contain coding for the 4 sec ring, 8 sec silence US sequence. However the astute reader will realise that many other types would work, and in fact we are only using 128 address locations and one bit of the 8 bit wide data byte stored in the eprom (D0) The eprom contents are shown in the table (below) it can be seen that the pink higlighted locations represent a "ring" and all others silence (read from top to bottom) Gating is achieved in the 4093 NAND gate, its output then inverted directly feeds a VMOS FET gate which switches the unregulated 15v rail onto the transformer primary.

The VMOS FET is preferred over a bipolar transistor etc here because of their power handling capacity and very low "on" state resistance (milliohms) which allows most of the +15v DC rail be available to the transformer winding. Fortunately these devices also have an internal reversed biased diode, b/w drain and source which protects them against failure from transient spikes (refer to manuf` data sheets).

The particular FET specified 2SK3296, I salvaged several from defunct P4 computer mother board (in power supply circuit). However suitable replacement types are easily available. I have used a 5000 ohm to 4 ohm loud-speaker transformer (in reverse - so to speak) to step up the voltage to the level necessary the make the bell solenoid actuate the armature (1 : 35 ratio) Simply remove the internals (circuit board, fan etc) and you have a 6" x 6" x 3" sized metal box with IEC entry connector and on/off mains switch etc - ready for re-use.

🔗 External reference