Watchdog Timer/Alarm

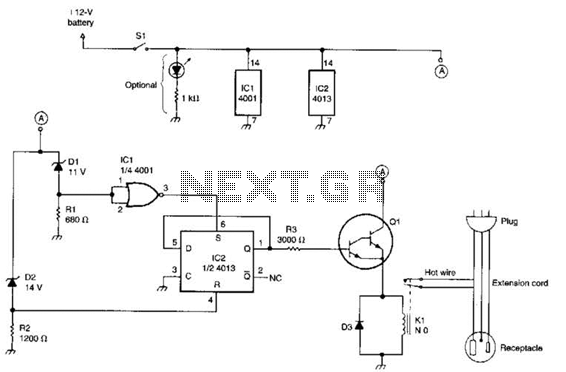

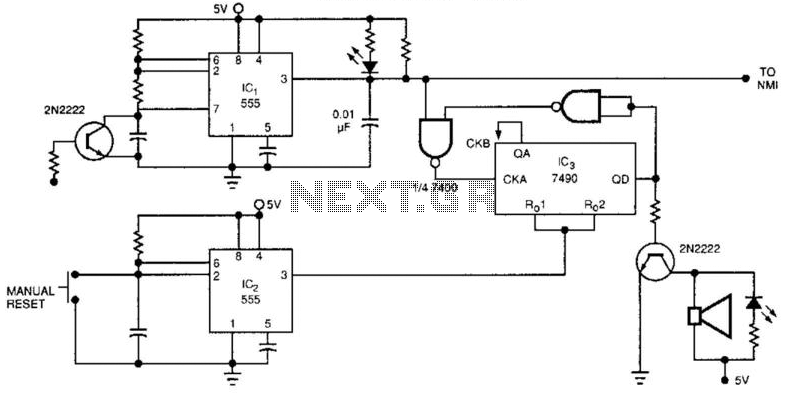

The watchdog timer includes a counter, IC3, alongside the standard retriggerable 555 timer, IC1. The counter will sound an audible alarm if the watchdog timer attempts to reset a specified number of times (8, in the case of the counter). The alarm serves as an indication that despite multiple reset attempts, the system has not successfully restarted and is non-operational. A second 555 timer, IC2, is utilized to reset the counter, IC3, for the duration of a manual system restart. The design can be altered to allow the system to reset the counter autonomously.

The described watchdog timer circuit is a critical component for monitoring the operational state of electronic systems. It employs a retriggerable 555 timer (IC1) to monitor system performance and a counter (IC3) to track the number of reset attempts. If the system fails to restart after eight attempts, the counter triggers an audible alarm, alerting users to a system failure.

IC1 operates in a monostable mode, where it generates a pulse each time it is triggered. This pulse is used to reset the counter, IC3. The counter is configured to count the number of reset attempts. Once the count reaches eight, it indicates a persistent failure, prompting the system to activate an alarm signal. This alarm can be implemented using a simple piezo buzzer or speaker, providing an audible notification of the issue.

The second 555 timer (IC2) plays a vital role in managing the reset process. It is configured to reset the counter (IC3) during manual restart procedures, ensuring that users have the opportunity to attempt a reset without triggering the alarm prematurely. The design can be further enhanced by integrating an automatic reset feature, allowing the system itself to reset the counter after a successful restart. This modification could improve the reliability of the circuit by minimizing unnecessary alarm activations.

In summary, this watchdog timer circuit is designed to enhance system reliability by monitoring operational status and providing alerts in case of failures. Its use of a retriggerable 555 timer and a counter allows for effective tracking of reset attempts, while the incorporation of an alarm system ensures that users are promptly informed of any critical failures. The watchdog timer contains a counter, IC3, in addition to the usual retriggerable 555 timer, ICl. The counter will so und an audible alarm if the watchdog timer trys to reset the a certain number of times (8, in the case of the counter). The alarm indicates that despite numerous resets, the system has failed to restart successfully, and the system is truly dead.

A second 555 timer, IC2, resets the counter, 1C3, for the duration of the manual system restart. The design could be modified so that system resets the counter. 🔗 External reference

The described watchdog timer circuit is a critical component for monitoring the operational state of electronic systems. It employs a retriggerable 555 timer (IC1) to monitor system performance and a counter (IC3) to track the number of reset attempts. If the system fails to restart after eight attempts, the counter triggers an audible alarm, alerting users to a system failure.

IC1 operates in a monostable mode, where it generates a pulse each time it is triggered. This pulse is used to reset the counter, IC3. The counter is configured to count the number of reset attempts. Once the count reaches eight, it indicates a persistent failure, prompting the system to activate an alarm signal. This alarm can be implemented using a simple piezo buzzer or speaker, providing an audible notification of the issue.

The second 555 timer (IC2) plays a vital role in managing the reset process. It is configured to reset the counter (IC3) during manual restart procedures, ensuring that users have the opportunity to attempt a reset without triggering the alarm prematurely. The design can be further enhanced by integrating an automatic reset feature, allowing the system itself to reset the counter after a successful restart. This modification could improve the reliability of the circuit by minimizing unnecessary alarm activations.

In summary, this watchdog timer circuit is designed to enhance system reliability by monitoring operational status and providing alerts in case of failures. Its use of a retriggerable 555 timer and a counter allows for effective tracking of reset attempts, while the incorporation of an alarm system ensures that users are promptly informed of any critical failures. The watchdog timer contains a counter, IC3, in addition to the usual retriggerable 555 timer, ICl. The counter will so und an audible alarm if the watchdog timer trys to reset the a certain number of times (8, in the case of the counter). The alarm indicates that despite numerous resets, the system has failed to restart successfully, and the system is truly dead.

A second 555 timer, IC2, resets the counter, 1C3, for the duration of the manual system restart. The design could be modified so that system resets the counter. 🔗 External reference