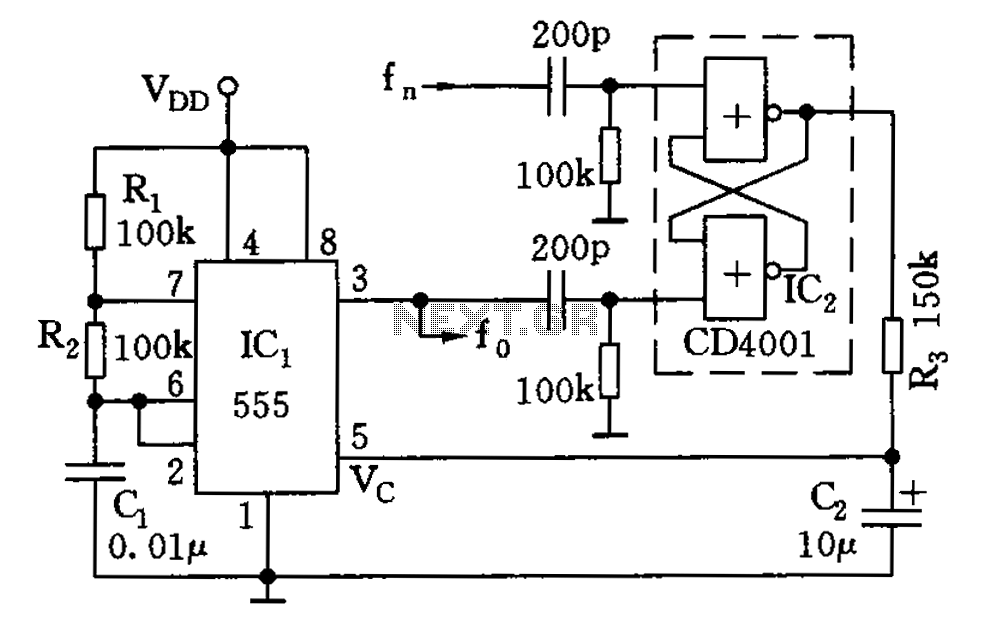

Clock synchronization oscillator circuit

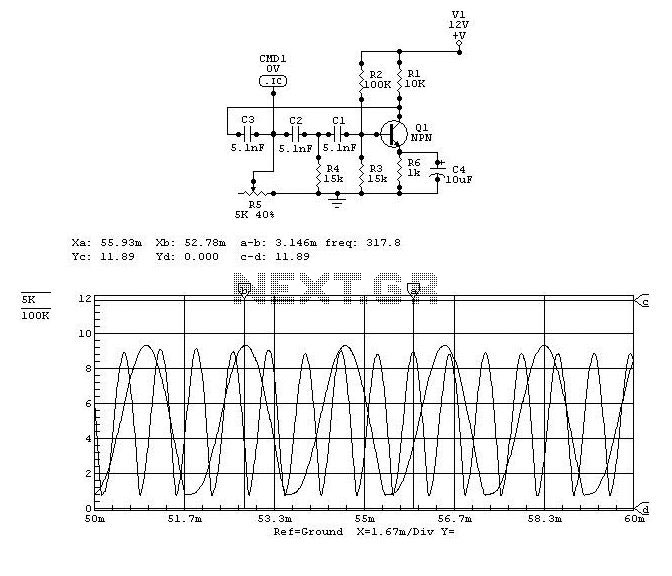

The circuit illustrated consists of a 555 timer along with resistors R1 and R2, and capacitor C1, forming a composition-controlled multivibrator. The oscillation frequency is influenced not only by the RC time constant but also by the adjustment of the control terminal's DC level. The output frequency from the 555 timer and the oscillation frequency are related to a common locking square wave output produced by an RS flip-flop. This output is processed through a low-pass filter. The RS flip-flop is constructed using two NOR gates from the CD4001 integrated circuit. When the RS flip-flop is in a locked state, the duty cycle of the output remains constant, thereby keeping the filtered DC level stable. If the oscillation frequency of the 555 timer increases significantly (or decreases), the duty cycle will increase, resulting in a corresponding rise in the DC control level, while a decrease in frequency will lead to the opposite effect.

The circuit described employs a 555 timer configured in astable mode, which generates a continuous square wave output. The frequency of oscillation is determined by the values of resistors R1 and R2, as well as capacitor C1, following the standard formula for a 555 timer in astable operation:

\[ f_o = \frac{1.44}{(R1 + 2R2) \cdot C1} \]

The control terminal, often labeled as pin 5 on the 555 timer, can be used to adjust the DC level of the output frequency. This adjustment allows for fine-tuning the oscillation frequency, enhancing the versatility of the circuit.

The output from the 555 timer is fed into an RS flip-flop, implemented using two NOR gates from the CD4001 IC. The RS flip-flop serves to lock the output signal, ensuring a stable duty cycle. The duty cycle is defined as the ratio of the time the output is high to the total period of the waveform. When the circuit is in a locked state, the duty cycle remains unchanged, which stabilizes the DC level produced by the low-pass filter.

The low-pass filter is crucial as it smooths out the square wave output from the RS flip-flop, providing a more stable DC voltage. The relationship between the oscillation frequency and the DC control level is significant; as the frequency increases, the duty cycle also increases, which in turn raises the DC level. Conversely, a decrease in frequency results in a lower duty cycle and a corresponding decrease in the DC level. This dynamic interaction between frequency, duty cycle, and DC control level is essential for applications requiring precise timing and control in electronic circuits.

Overall, this circuit design showcases the integration of a 555 timer, RS flip-flop, and low-pass filtering to achieve a stable multivibrator output, making it suitable for various timing and control applications in electronics.As illustrated, 555 and R1, R2, C1 composition controlled multivibrator, its oscillation frequency in addition to the RC time constant related to, but also by the control termi nal of the DC level is adjusted. While the DC level from the reference frequency f. 555 output and the oscillation frequency fo Nfn common locking square wave output of RS flip-flop, after the low-pass filtered to produce. CD4001 two NOR gates as RS flip-flop, RS flip-flop in the locked case, the duty cycle of the output unchanged, thus filtered DC level unchanged.

If the oscillation frequency f0 of 555 to a high drift (or fn fall), the duty increase, DC control level will be a corresponding increase in frequency will decline; and vice versa.

The circuit described employs a 555 timer configured in astable mode, which generates a continuous square wave output. The frequency of oscillation is determined by the values of resistors R1 and R2, as well as capacitor C1, following the standard formula for a 555 timer in astable operation:

\[ f_o = \frac{1.44}{(R1 + 2R2) \cdot C1} \]

The control terminal, often labeled as pin 5 on the 555 timer, can be used to adjust the DC level of the output frequency. This adjustment allows for fine-tuning the oscillation frequency, enhancing the versatility of the circuit.

The output from the 555 timer is fed into an RS flip-flop, implemented using two NOR gates from the CD4001 IC. The RS flip-flop serves to lock the output signal, ensuring a stable duty cycle. The duty cycle is defined as the ratio of the time the output is high to the total period of the waveform. When the circuit is in a locked state, the duty cycle remains unchanged, which stabilizes the DC level produced by the low-pass filter.

The low-pass filter is crucial as it smooths out the square wave output from the RS flip-flop, providing a more stable DC voltage. The relationship between the oscillation frequency and the DC control level is significant; as the frequency increases, the duty cycle also increases, which in turn raises the DC level. Conversely, a decrease in frequency results in a lower duty cycle and a corresponding decrease in the DC level. This dynamic interaction between frequency, duty cycle, and DC control level is essential for applications requiring precise timing and control in electronic circuits.

Overall, this circuit design showcases the integration of a 555 timer, RS flip-flop, and low-pass filtering to achieve a stable multivibrator output, making it suitable for various timing and control applications in electronics.As illustrated, 555 and R1, R2, C1 composition controlled multivibrator, its oscillation frequency in addition to the RC time constant related to, but also by the control termi nal of the DC level is adjusted. While the DC level from the reference frequency f. 555 output and the oscillation frequency fo Nfn common locking square wave output of RS flip-flop, after the low-pass filtered to produce. CD4001 two NOR gates as RS flip-flop, RS flip-flop in the locked case, the duty cycle of the output unchanged, thus filtered DC level unchanged.

If the oscillation frequency f0 of 555 to a high drift (or fn fall), the duty increase, DC control level will be a corresponding increase in frequency will decline; and vice versa.

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713