Auto Turn-Off Alarm With 8-Minute Delay

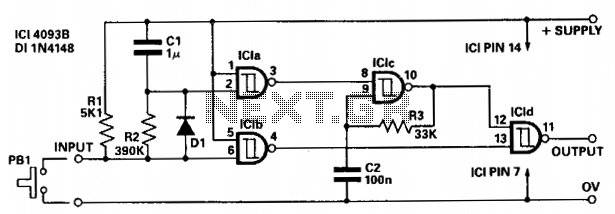

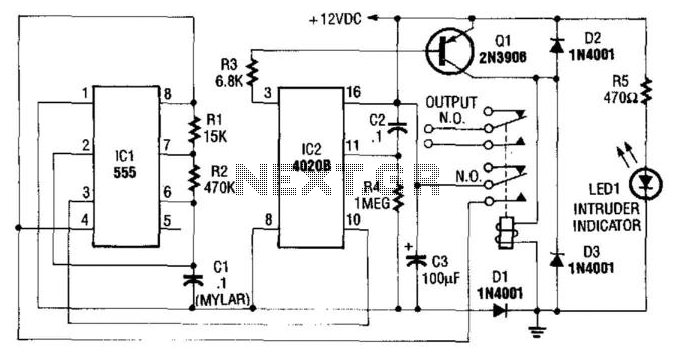

This circuit utilizes a NE555 timer and a CD4020B. When +12 Vdc is applied to the circuit, the output of IC2 is set low via C2, which activates the relay and IC1, functioning as a pulse generator. IC1 generates pulses that drive the counter IC2. After 8192 clock cycles, the output of IC2 (pin 3) goes high, deactivating Q2 and completing the cycle.

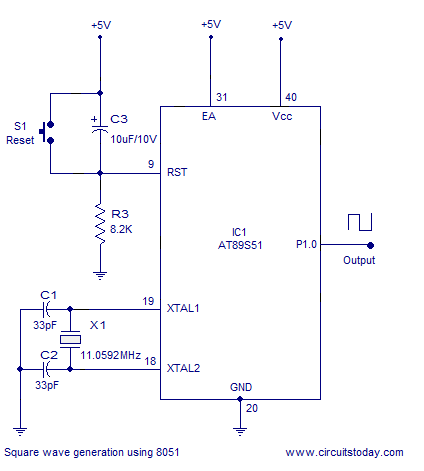

The circuit design incorporates a NE555 timer configured in astable mode to produce a continuous square wave output. This output serves as the clock signal for the CD4020B binary counter, which is a 14-stage ripple counter capable of counting up to 16384. The pulse frequency generated by the NE555 timer can be adjusted through the selection of external resistors and capacitors connected to its timing pins.

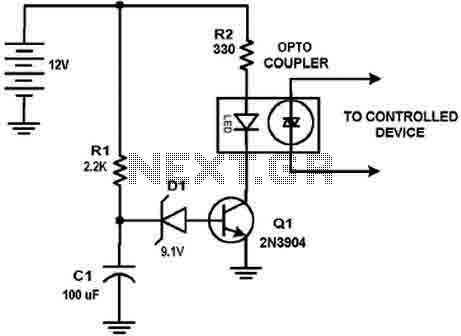

When the circuit is powered with a +12 Vdc supply, the timing capacitor C2 initially charges, causing the output of the CD4020B (IC2) to be low. This low output state activates a relay, allowing current to flow through the relay coil, which in turn can control a larger load. The NE555 timer (IC1) produces a series of pulses that increment the count in the CD4020B. Each pulse corresponds to a clock cycle, and after 8192 pulses, the output at pin 3 of IC2 transitions to a high state.

This transition from low to high at pin 3 of the CD4020B serves as a control signal that turns off transistor Q2, thereby deactivating the relay. The relay's deactivation may be used to switch off a load or to signal the completion of a specific operation. The overall design allows for precise timing and control, making it suitable for applications where sequential operations are required based on a defined count or timing interval.

Proper selection of components, including the NE555 timer's resistors and capacitors, as well as the relay specifications, is crucial for ensuring reliable operation and desired performance characteristics of the circuit. This circuit uses a NE555 timer and CD4020B. When +12 Vdc is applied to the circuit, the output of IC2 is set low via C2, which turns on the relay, and IC1, a pulse generator. IC1 pulses counter IC2. After 8192 clocks, IC2 output (pin 3) goes high, cuts off Q2, and completes the cycle.

The circuit design incorporates a NE555 timer configured in astable mode to produce a continuous square wave output. This output serves as the clock signal for the CD4020B binary counter, which is a 14-stage ripple counter capable of counting up to 16384. The pulse frequency generated by the NE555 timer can be adjusted through the selection of external resistors and capacitors connected to its timing pins.

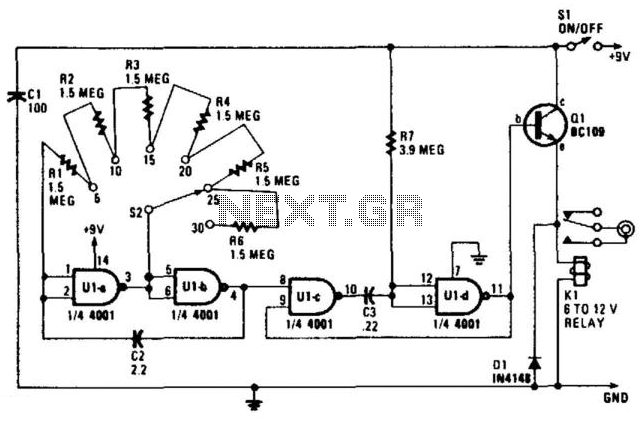

When the circuit is powered with a +12 Vdc supply, the timing capacitor C2 initially charges, causing the output of the CD4020B (IC2) to be low. This low output state activates a relay, allowing current to flow through the relay coil, which in turn can control a larger load. The NE555 timer (IC1) produces a series of pulses that increment the count in the CD4020B. Each pulse corresponds to a clock cycle, and after 8192 pulses, the output at pin 3 of IC2 transitions to a high state.

This transition from low to high at pin 3 of the CD4020B serves as a control signal that turns off transistor Q2, thereby deactivating the relay. The relay's deactivation may be used to switch off a load or to signal the completion of a specific operation. The overall design allows for precise timing and control, making it suitable for applications where sequential operations are required based on a defined count or timing interval.

Proper selection of components, including the NE555 timer's resistors and capacitors, as well as the relay specifications, is crucial for ensuring reliable operation and desired performance characteristics of the circuit. This circuit uses a NE555 timer and CD4020B. When +12 Vdc is applied to the circuit, the output of IC2 is set low via C2, which turns on the relay, and IC1, a pulse generator. IC1 pulses counter IC2. After 8192 clocks, IC2 output (pin 3) goes high, cuts off Q2, and completes the cycle.