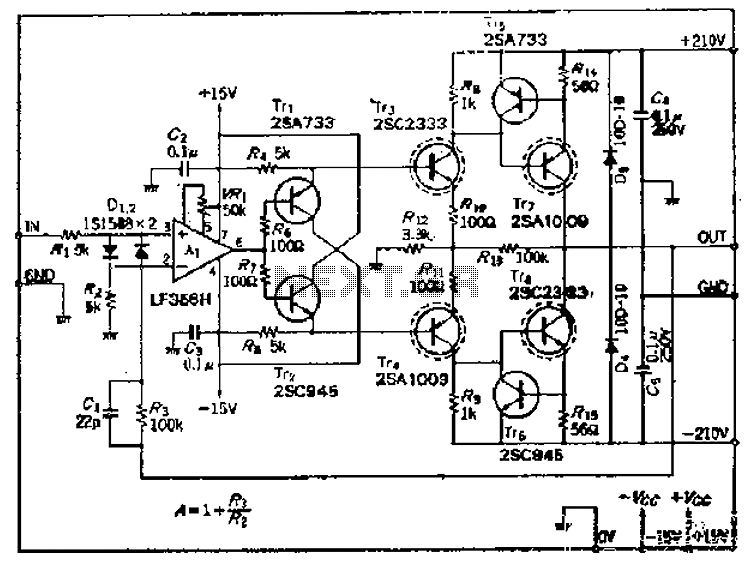

Discrete Voltage Inverter

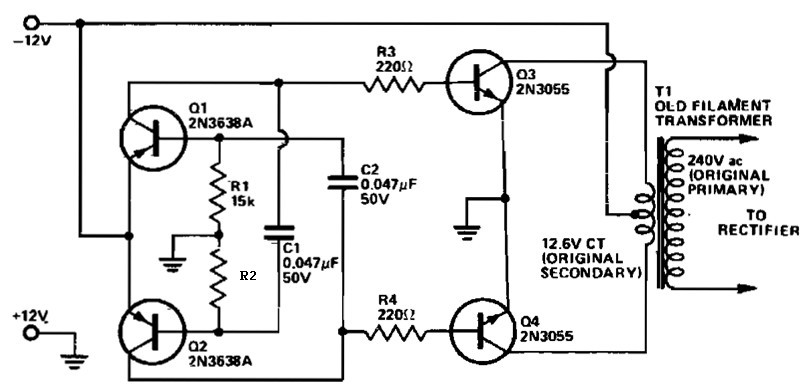

The circuit in the diagram generates a negative voltage without using integrated circuits. It utilizes five n-p-n transistors driven by an approximately 1 kHz TTL clock. When the clock input is high, transistors T1 and T2 connect capacitor C1 to the supply voltage, UIN, typically 5 V. During this phase, transistor T5 conducts, causing transistors T3 and T4 to remain off. When the clock input goes low, T5 is turned off, and transistors T3 and T4 are activated via pull-up resistor R6 and either R4 or R5. This action shares the charge on C1 between this capacitor and C2. Since the positive terminal of C2 is at ground potential, its negative terminal must become negative with respect to earth. The high level of the clock input must be similar to the positive input voltage, UIN; otherwise, T1 cannot be activated. The clock frequency should be around 1 kHz to maintain a duty cycle ratio of 1:1. Modifying this ratio results in a different negative output voltage, which will always be less than that achieved with a 1:1 ratio.

The described circuit operates as a negative voltage generator using discrete components, specifically five n-p-n transistors. The essential components include transistors T1, T2, T3, T4, and T5, along with capacitors C1 and C2, resistors R4, R5, and R6, and a TTL clock signal. The operation begins with the clock signal oscillating at approximately 1 kHz, which is critical for the timing of the transistors' switching actions.

When the clock signal is high, T1 and T2 are activated, allowing capacitor C1 to charge from the supply voltage, UIN. This charging phase is crucial as it sets up the initial conditions for generating the negative voltage. The conduction of T5 during this period ensures that T3 and T4 remain off, preventing any premature discharge of the capacitors.

As the clock transitions to a low state, T5 is turned off, which triggers T3 and T4 to turn on through the pull-up resistor R6 and either R4 or R5. This switching action leads to the redistribution of charge between capacitors C1 and C2. Given that the positive terminal of C2 is grounded, this results in a negative voltage appearing at the negative terminal of C2 relative to ground.

The design requires that the high level of the clock input matches or exceeds the supply voltage, UIN, to ensure that T1 can effectively switch on. This condition is vital for the proper functioning of the circuit. The 1 kHz frequency is selected to achieve a duty cycle of 1:1, which is optimal for generating the desired negative voltage output. Adjustments to the duty cycle ratio can yield varying levels of negative voltage, but it is important to note that the output will always be lower than that produced with a 1:1 ratio. This circuit provides an efficient method for generating negative voltages without the need for integrated circuits, showcasing the utility of discrete transistor components in voltage regulation applications.The circuit in the diagram enables a negative voltage to be derived without the use of integrated circuits. Instead, it uses five n-p-n transistors that are driven by a 1 kHz (approx) TTL clock. When the clock input is high, transistors T1 and T2 link capacitor C1 to the supply voltage, UIN, which typically is 5 V.

During this process, transistor T5 conducts so that T3 and T4 are off. When the clock input is low, T5 is cut off, whereupon transistors T3 and T4 are switched on via pull-up resistor R6 and either R4 or R5. This results in the charge on C1 being shared between this capacitor and C2 Since the +ve terminal of C2 is at ground potential, its ve terminal must become negative w.

r. t. earth. The high level at the clock input must be of the same order as the positive input voltage, UIN, otherwise T1 cannot be switched on. The clock frequency should be around 1 kHz to ensure a duty cycle ratio of 1:1. Altering the ratio results in a different level of negative output voltage, but this is always smaller than that with a ratio of 1:1.

🔗 External reference

The described circuit operates as a negative voltage generator using discrete components, specifically five n-p-n transistors. The essential components include transistors T1, T2, T3, T4, and T5, along with capacitors C1 and C2, resistors R4, R5, and R6, and a TTL clock signal. The operation begins with the clock signal oscillating at approximately 1 kHz, which is critical for the timing of the transistors' switching actions.

When the clock signal is high, T1 and T2 are activated, allowing capacitor C1 to charge from the supply voltage, UIN. This charging phase is crucial as it sets up the initial conditions for generating the negative voltage. The conduction of T5 during this period ensures that T3 and T4 remain off, preventing any premature discharge of the capacitors.

As the clock transitions to a low state, T5 is turned off, which triggers T3 and T4 to turn on through the pull-up resistor R6 and either R4 or R5. This switching action leads to the redistribution of charge between capacitors C1 and C2. Given that the positive terminal of C2 is grounded, this results in a negative voltage appearing at the negative terminal of C2 relative to ground.

The design requires that the high level of the clock input matches or exceeds the supply voltage, UIN, to ensure that T1 can effectively switch on. This condition is vital for the proper functioning of the circuit. The 1 kHz frequency is selected to achieve a duty cycle of 1:1, which is optimal for generating the desired negative voltage output. Adjustments to the duty cycle ratio can yield varying levels of negative voltage, but it is important to note that the output will always be lower than that produced with a 1:1 ratio. This circuit provides an efficient method for generating negative voltages without the need for integrated circuits, showcasing the utility of discrete transistor components in voltage regulation applications.The circuit in the diagram enables a negative voltage to be derived without the use of integrated circuits. Instead, it uses five n-p-n transistors that are driven by a 1 kHz (approx) TTL clock. When the clock input is high, transistors T1 and T2 link capacitor C1 to the supply voltage, UIN, which typically is 5 V.

During this process, transistor T5 conducts so that T3 and T4 are off. When the clock input is low, T5 is cut off, whereupon transistors T3 and T4 are switched on via pull-up resistor R6 and either R4 or R5. This results in the charge on C1 being shared between this capacitor and C2 Since the +ve terminal of C2 is at ground potential, its ve terminal must become negative w.

r. t. earth. The high level at the clock input must be of the same order as the positive input voltage, UIN, otherwise T1 cannot be switched on. The clock frequency should be around 1 kHz to ensure a duty cycle ratio of 1:1. Altering the ratio results in a different level of negative output voltage, but this is always smaller than that with a ratio of 1:1.

🔗 External reference