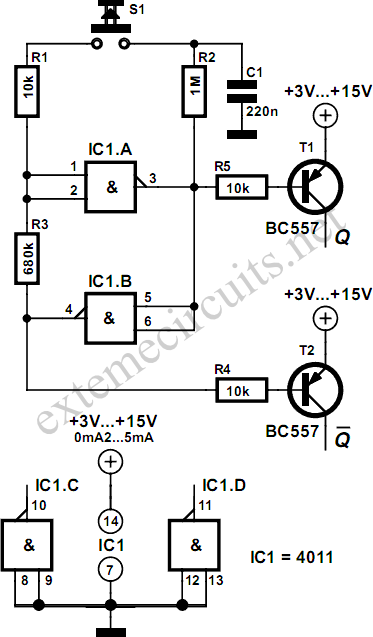

Flip-Flop Using CMOS NAND Gates

Using just two NAND or inverter gates, it is possible to build a D-type (or toggle) flip-flop with a push-button input. At power-up, the output of gate N2 is at a logical 1, ensuring that transistor T2 is switched off. When the push-button is pressed, the output of N2 changes to a logical 0, and transistor T2 conducts. The coupling between N1 and N2 ensures that the output of N1 will always be the inverse of N2, so T1 and T2 will always be in opposite states and will flip each time the push-button is pressed. In some cases, it is possible to omit T1 and T2 and use the outputs of N2 and N1 to drive external circuitry directly, but only if the loading on these outputs is low enough. The 4000 series CMOS family can source/sink a maximum of 0.5 mA (at 5 V), so for safety, it is best to use these open-collector configured transistor buffers. This circuit is particularly useful if there are some unused gates left over in a circuit design, avoiding the need to add a dedicated flip-flop IC. It is important to remember that all other unused CMOS gates must have their inputs connected to either the positive or ground rail. The supply voltage can range from 3 V to 15 V for CMOS ICs, and the current consumed by this circuit is between 0.2 mA and 5 mA (no load).

The described circuit utilizes two NAND gates or inverters to create a simple D-type flip-flop configuration with a push-button mechanism for toggling its state. Upon initial power-up, the output of the second gate (N2) is set to a high logic level (1), which keeps the output of the associated transistor (T2) in an off state. When the push-button is activated, it causes N2 to transition to a low logic level (0), resulting in T2 turning on and allowing current to flow.

The interconnection between the two gates (N1 and N2) is crucial as it ensures that the output of N1 is always the logical inverse of N2. This complementary behavior guarantees that the two transistors (T1 and T2) are never in the same state; one is always conducting while the other is off. This toggling action occurs with each press of the push-button, effectively allowing the circuit to function as a flip-flop.

In scenarios where output load is minimal, it is feasible to directly connect the outputs of N1 and N2 to external circuits, thereby eliminating the need for the transistors. However, caution is advised since the 4000 series CMOS devices have a limitation of sourcing or sinking a maximum of 0.5 mA at a supply voltage of 5 V. Therefore, implementing open-collector transistor buffers is recommended for enhanced reliability and safety.

This configuration is particularly advantageous for designers who may have surplus unused gates in their circuit designs, as it negates the necessity of incorporating a dedicated flip-flop integrated circuit. It is also critical to connect the inputs of any unused CMOS gates to either the positive supply or ground to prevent floating inputs, which can lead to unpredictable behavior.

The circuit operates effectively over a supply voltage range of 3 V to 15 V, with the current consumption varying between 0.2 mA and 5 mA when there is no load present. This flexibility in supply voltage and low current draw makes the circuit suitable for various low-power applications, ensuring efficient operation within the specified parameters.Using just two NAND or inverter gates its possible to build a D type (or toggle`)‚ip-‚op with a push-button input. At power-up the output of gate N2 is at a logical 1`, ensuring that transistor T2 is switched off. When the push-button is pressed the output of N2 changes to a logical 0` and transistor T2 conducts. The coupling between N1 and N 2 ensures that the output of N1 will always be the inverse of N2 so T1 and T2 will always be in opposite states and will flip each time the push-button is pressed. In some cases it is possible to omit T1 and T2 and use the outputs of N2 and N1 to drive external circuitry directly but only if the loading on these outputs is low enough.

The 4000 series CMOS family can source/sink a maximum of 0. 5mA (at 5 V) so for the sake of safety its best to use these open-collector congured transistor buffers. This circuit is particularly useful if you have some unused gates left over in a circuit design, avoiding the need to add a dedicated flip-flop IC.

It is worth remembering that all other unused CMOS gates must have their inputs connected to either the positive or ground rail. The supply voltage can be in the range 3 V to 15 V for CMOS ICs and the current taken by this circuit is between 0.

2 mA and 5 mA (no load). 🔗 External reference

The described circuit utilizes two NAND gates or inverters to create a simple D-type flip-flop configuration with a push-button mechanism for toggling its state. Upon initial power-up, the output of the second gate (N2) is set to a high logic level (1), which keeps the output of the associated transistor (T2) in an off state. When the push-button is activated, it causes N2 to transition to a low logic level (0), resulting in T2 turning on and allowing current to flow.

The interconnection between the two gates (N1 and N2) is crucial as it ensures that the output of N1 is always the logical inverse of N2. This complementary behavior guarantees that the two transistors (T1 and T2) are never in the same state; one is always conducting while the other is off. This toggling action occurs with each press of the push-button, effectively allowing the circuit to function as a flip-flop.

In scenarios where output load is minimal, it is feasible to directly connect the outputs of N1 and N2 to external circuits, thereby eliminating the need for the transistors. However, caution is advised since the 4000 series CMOS devices have a limitation of sourcing or sinking a maximum of 0.5 mA at a supply voltage of 5 V. Therefore, implementing open-collector transistor buffers is recommended for enhanced reliability and safety.

This configuration is particularly advantageous for designers who may have surplus unused gates in their circuit designs, as it negates the necessity of incorporating a dedicated flip-flop integrated circuit. It is also critical to connect the inputs of any unused CMOS gates to either the positive supply or ground to prevent floating inputs, which can lead to unpredictable behavior.

The circuit operates effectively over a supply voltage range of 3 V to 15 V, with the current consumption varying between 0.2 mA and 5 mA when there is no load present. This flexibility in supply voltage and low current draw makes the circuit suitable for various low-power applications, ensuring efficient operation within the specified parameters.Using just two NAND or inverter gates its possible to build a D type (or toggle`)‚ip-‚op with a push-button input. At power-up the output of gate N2 is at a logical 1`, ensuring that transistor T2 is switched off. When the push-button is pressed the output of N2 changes to a logical 0` and transistor T2 conducts. The coupling between N1 and N 2 ensures that the output of N1 will always be the inverse of N2 so T1 and T2 will always be in opposite states and will flip each time the push-button is pressed. In some cases it is possible to omit T1 and T2 and use the outputs of N2 and N1 to drive external circuitry directly but only if the loading on these outputs is low enough.

The 4000 series CMOS family can source/sink a maximum of 0. 5mA (at 5 V) so for the sake of safety its best to use these open-collector congured transistor buffers. This circuit is particularly useful if you have some unused gates left over in a circuit design, avoiding the need to add a dedicated flip-flop IC.

It is worth remembering that all other unused CMOS gates must have their inputs connected to either the positive or ground rail. The supply voltage can be in the range 3 V to 15 V for CMOS ICs and the current taken by this circuit is between 0.

2 mA and 5 mA (no load). 🔗 External reference