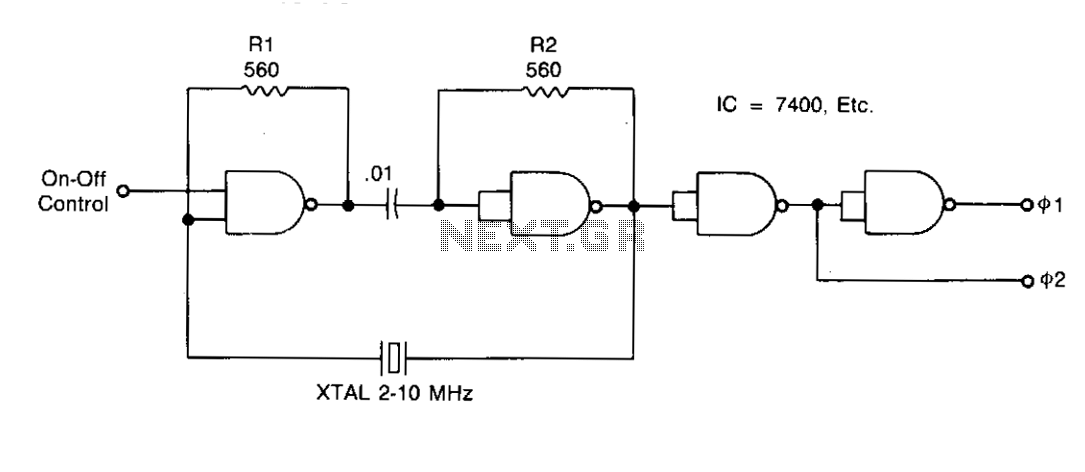

IC-compatible crystal oscillator

Resistors R1 and R2 stabilize the temperature of the NAND gates and ensure that the gates operate within a linear region during startup. Capacitor C1 acts as a DC block and must have an impedance lower than Vw at the operating frequency. The crystal operates in a series-resonant mode, requiring low series resistance; AT-cut crystals in the 1 to 10 MHz range are suitable. The output waveform exhibits nearly a 50% duty cycle, with rise times limited by the chip. The circuit functions effectively within a temperature range of 0°C to 70°C.

The described circuit utilizes resistors R1 and R2 to maintain stable operating conditions for the NAND gates, which are crucial for reliable digital logic performance. These resistors help mitigate temperature-induced variations, ensuring consistent behavior across the specified temperature range. The selection of resistors should consider their thermal coefficients to maintain stability as environmental conditions change.

Capacitor C1 serves the critical function of decoupling DC components from the AC signals within the circuit. Its impedance must be carefully chosen to ensure it does not adversely affect the frequency response, particularly at the operating frequency. A low impedance value at the intended frequency will facilitate effective signal transmission while blocking any DC offset that may interfere with the logic levels of the NAND gates.

The crystal's operation in a series-resonant mode is essential for achieving the desired oscillation frequency. The use of AT-cut crystals is advantageous due to their inherent stability and low series resistance, making them ideal for applications in the 1 to 10 MHz frequency range. This low series resistance minimizes power loss and enhances the overall efficiency of the oscillator circuit.

The output waveform characteristics, including a nearly 50% duty cycle, indicate that the circuit is designed for balanced switching behavior, which is critical in digital applications to ensure proper timing and signal integrity. The chip-limited rise times suggest that the design may incorporate specific components to manage signal transitions, which can help reduce electromagnetic interference and improve overall performance.

Operating effectively from 0°C to 70°C indicates that the circuit is designed for typical commercial applications, where temperature variations are expected. Proper thermal management and component selection are essential to ensure reliable operation within this range, and careful consideration should be given to the thermal characteristics of all components involved in the circuit.Resistors Rl and R2 temperature-stabilize the NAND gates; they also ensure that the gates are in a linear region for starting. Capacitor CI is a dc block; it must have less than Vw ohm impedance at the operating frequency. The crystal runs in a series-resonant mode. Its series resistance must be low; AT-cut crystals for the 1- to 10-MHz range work well. The output waveshape has nearly a 50% duty cycle, with chip-limited rise times. The circuit starts well from 0° to 70°C.

The described circuit utilizes resistors R1 and R2 to maintain stable operating conditions for the NAND gates, which are crucial for reliable digital logic performance. These resistors help mitigate temperature-induced variations, ensuring consistent behavior across the specified temperature range. The selection of resistors should consider their thermal coefficients to maintain stability as environmental conditions change.

Capacitor C1 serves the critical function of decoupling DC components from the AC signals within the circuit. Its impedance must be carefully chosen to ensure it does not adversely affect the frequency response, particularly at the operating frequency. A low impedance value at the intended frequency will facilitate effective signal transmission while blocking any DC offset that may interfere with the logic levels of the NAND gates.

The crystal's operation in a series-resonant mode is essential for achieving the desired oscillation frequency. The use of AT-cut crystals is advantageous due to their inherent stability and low series resistance, making them ideal for applications in the 1 to 10 MHz frequency range. This low series resistance minimizes power loss and enhances the overall efficiency of the oscillator circuit.

The output waveform characteristics, including a nearly 50% duty cycle, indicate that the circuit is designed for balanced switching behavior, which is critical in digital applications to ensure proper timing and signal integrity. The chip-limited rise times suggest that the design may incorporate specific components to manage signal transitions, which can help reduce electromagnetic interference and improve overall performance.

Operating effectively from 0°C to 70°C indicates that the circuit is designed for typical commercial applications, where temperature variations are expected. Proper thermal management and component selection are essential to ensure reliable operation within this range, and careful consideration should be given to the thermal characteristics of all components involved in the circuit.Resistors Rl and R2 temperature-stabilize the NAND gates; they also ensure that the gates are in a linear region for starting. Capacitor CI is a dc block; it must have less than Vw ohm impedance at the operating frequency. The crystal runs in a series-resonant mode. Its series resistance must be low; AT-cut crystals for the 1- to 10-MHz range work well. The output waveshape has nearly a 50% duty cycle, with chip-limited rise times. The circuit starts well from 0° to 70°C.