Masochists Video Card Circuit

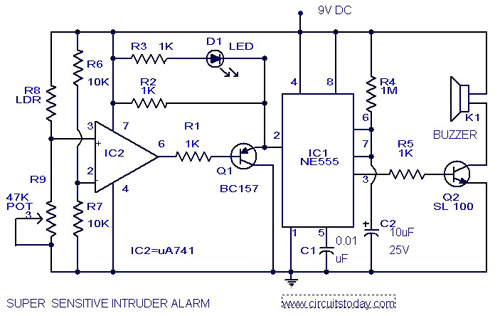

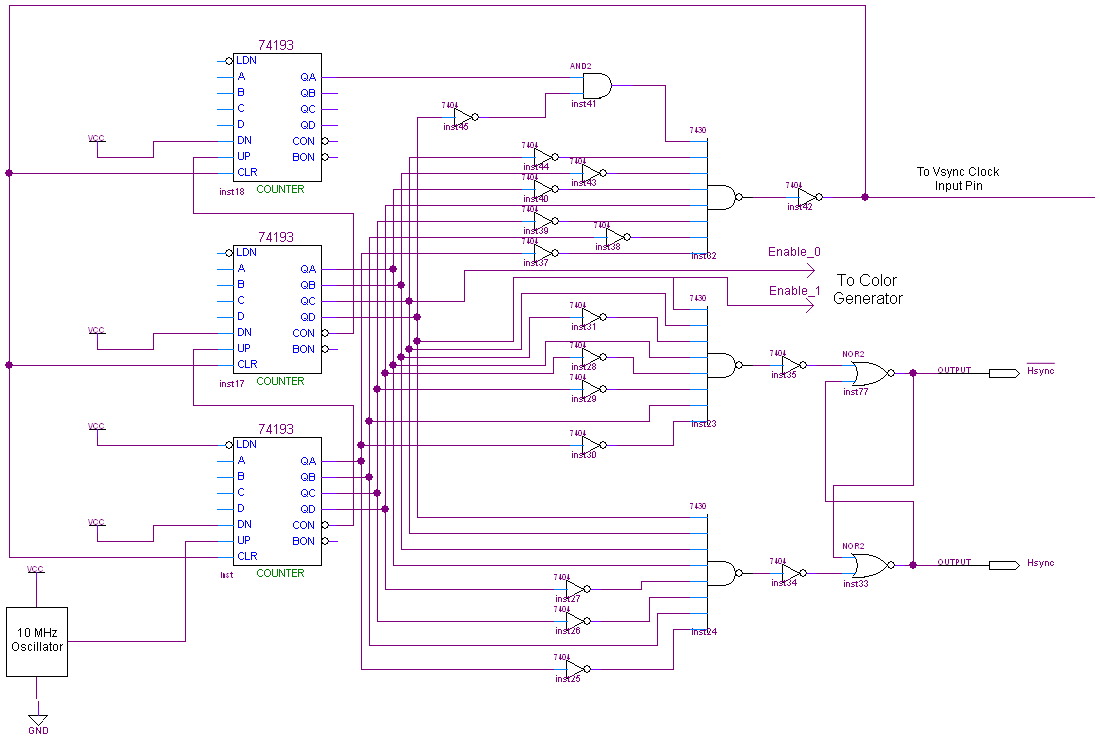

The complete schematic for this project is quite extensive. To view it, please click the image below. Due to its size, the explanation of the connections is divided into three sections: the Hsync Generator, Vsync Generator, and Color Generator. The Hsync circuit employs three 4-bit counters that count up to specific values, triggering the Hsync signal and providing a clear signal to reset the counter to zero. A 10 MHz crystal oscillator feeds into the first 4-bit counter, which increments its count. The carry output from the first counter links to the second counter, allowing it to continue counting, and the same applies to the third counter. The three specific values of interest for the 7430 8-input NAND gates are 210 (0b11010010), 242 (0b11110010), and 264 (0b100001000). The value 210 activates the Hsync signal, setting it to 1; 242 resets it to 0; and 264 serves as the clear signal, instructing the counters to restart from zero. Hex inverters are utilized to ensure the input to the 7430 NAND gate receives "11111111" for each designated value that triggers Hsync and Clear. AND gates are employed for values exceeding 8 bits, as the 7430 has an 8-bit limitation. The R/G/B color output must not be continuously active; therefore, it is enabled only when VGA timing allows for color signals. These signals are then input into the color generator as color enable signals.

The schematic comprises several critical components that work in conjunction to generate synchronization signals and color outputs for a VGA interface. The Hsync Generator is crucial for generating horizontal synchronization signals, which are essential for displaying images on a monitor. The three 4-bit counters are configured to count clock cycles produced by the 10 MHz oscillator. As the counters increment, they reach specific thresholds that correspond to the timing requirements of the VGA standard.

The 7430 NAND gates play a pivotal role in determining the state of the Hsync signal. When the first counter reaches 210, the Hsync signal is activated, indicating the start of a new horizontal scan line. The subsequent value of 242 is crucial for resetting the signal, ensuring that the display timing remains accurate. The clear signal at 264 resets the counters, allowing for continuous operation without overflow or timing errors.

Hex inverters are strategically placed to maintain a stable logic level at the inputs of the NAND gates, ensuring that the logic conditions for triggering the Hsync signal are met. The use of AND gates is necessary for handling any values that exceed the 8-bit capacity of the 7430, thereby ensuring that the system can accommodate the full range of required values without losing synchronization.

Furthermore, the Color Generator is designed to manage the R/G/B signals effectively. The timing of these signals is critical; they must be enabled only during the appropriate segments of the VGA signal to prevent artifacts or incorrect colors from being displayed. The color enable signals ensure that the color data is only sent when the Hsync and Vsync signals indicate that it is valid to do so, maintaining the integrity of the visual output.

Overall, this schematic integrates various components to achieve a robust VGA signal generation system, ensuring precise timing and accurate color representation on the display.The full schematic for this project is really, really big so if you want to see it, go ahead and click the picture below. Since the schematic is so big I split the explanation of how things are connected together into three sections.

The Hsync Generator, Vsync Generator and Color Generator. The Hsync circuit uses 3x 4-bit counters to count up to specific values that trigger the Hsync signal as well as a clear signal to reset the counter value to 0. A 10 MHz crystal oscillator is input to the first 4-bit counter which counts up. The carry bit from the first counter is connected to the 2nd counter so that the 2nd counter will continue counting upward, likewise for the 3rd counter.

210 (0b11010010), 242 (0b11110010) and 264 (0b100001000) are the three unique values that the 7430 8-input NAND gates are looking for. 210 will trigger the Hsync signal to set to 1, 242 triggers it to reset to 0 and 264 is the clear signal which tells the counters to start counting from 0 again.

Some hex inverters are used to make sure the input into the 7430 NAND gate is "11111111" for each of the specific values we want to trigger Hsync and Clear at. AND gates are used whenever the value is larger than 8 bits, since the 7430 maxes out at 8-bits. Since the R/G/B color output cannot always be active, we need to make sure it is only enabled when the VGA timing allows for color signals to be active.

These two signals are fed into the color generator as color enable signals. 🔗 External reference

The schematic comprises several critical components that work in conjunction to generate synchronization signals and color outputs for a VGA interface. The Hsync Generator is crucial for generating horizontal synchronization signals, which are essential for displaying images on a monitor. The three 4-bit counters are configured to count clock cycles produced by the 10 MHz oscillator. As the counters increment, they reach specific thresholds that correspond to the timing requirements of the VGA standard.

The 7430 NAND gates play a pivotal role in determining the state of the Hsync signal. When the first counter reaches 210, the Hsync signal is activated, indicating the start of a new horizontal scan line. The subsequent value of 242 is crucial for resetting the signal, ensuring that the display timing remains accurate. The clear signal at 264 resets the counters, allowing for continuous operation without overflow or timing errors.

Hex inverters are strategically placed to maintain a stable logic level at the inputs of the NAND gates, ensuring that the logic conditions for triggering the Hsync signal are met. The use of AND gates is necessary for handling any values that exceed the 8-bit capacity of the 7430, thereby ensuring that the system can accommodate the full range of required values without losing synchronization.

Furthermore, the Color Generator is designed to manage the R/G/B signals effectively. The timing of these signals is critical; they must be enabled only during the appropriate segments of the VGA signal to prevent artifacts or incorrect colors from being displayed. The color enable signals ensure that the color data is only sent when the Hsync and Vsync signals indicate that it is valid to do so, maintaining the integrity of the visual output.

Overall, this schematic integrates various components to achieve a robust VGA signal generation system, ensuring precise timing and accurate color representation on the display.The full schematic for this project is really, really big so if you want to see it, go ahead and click the picture below. Since the schematic is so big I split the explanation of how things are connected together into three sections.

The Hsync Generator, Vsync Generator and Color Generator. The Hsync circuit uses 3x 4-bit counters to count up to specific values that trigger the Hsync signal as well as a clear signal to reset the counter value to 0. A 10 MHz crystal oscillator is input to the first 4-bit counter which counts up. The carry bit from the first counter is connected to the 2nd counter so that the 2nd counter will continue counting upward, likewise for the 3rd counter.

210 (0b11010010), 242 (0b11110010) and 264 (0b100001000) are the three unique values that the 7430 8-input NAND gates are looking for. 210 will trigger the Hsync signal to set to 1, 242 triggers it to reset to 0 and 264 is the clear signal which tells the counters to start counting from 0 again.

Some hex inverters are used to make sure the input into the 7430 NAND gate is "11111111" for each of the specific values we want to trigger Hsync and Clear at. AND gates are used whenever the value is larger than 8 bits, since the 7430 maxes out at 8-bits. Since the R/G/B color output cannot always be active, we need to make sure it is only enabled when the VGA timing allows for color signals to be active.

These two signals are fed into the color generator as color enable signals. 🔗 External reference