Nathans Z80 Project Mark 2

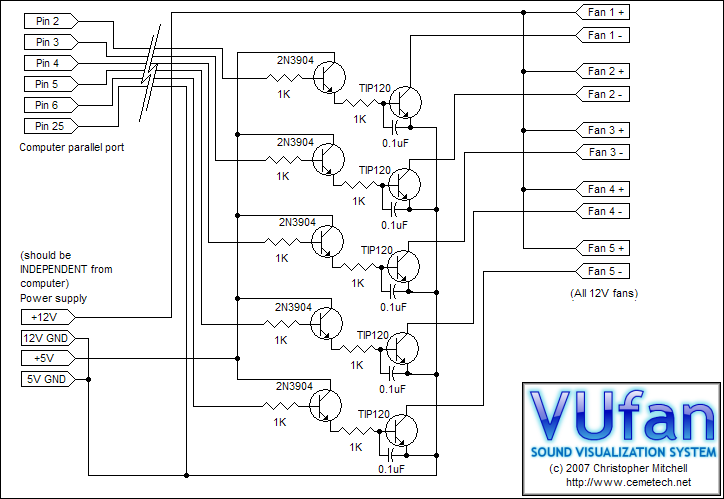

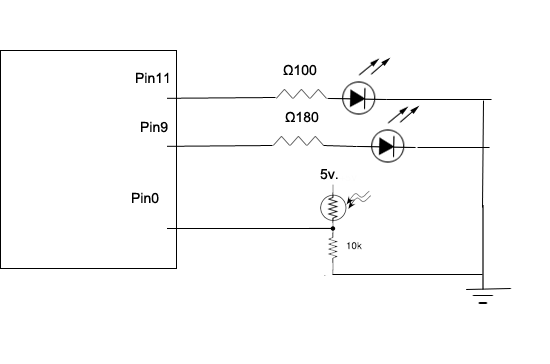

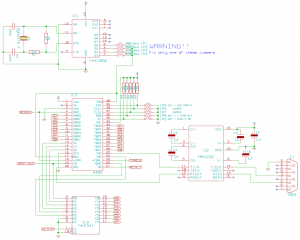

The primary requirement was to establish an output display and an alpha-numeric input system. A straightforward solution involved implementing a UART connected to a device featuring a screen and keyboard that operates a serial terminal. Although the existing PIC in the system could serve as a UART, it was determined that utilizing it as a fast DMA controller would be more advantageous. A 6402 UART chip, compatible with the vintage Z80 CPU, was selected as the core of the UART peripheral. The UART system comprises three peripheral chips: a 74HC4060 clock/divider chip, a MAX232 RS232 level shifter, and a 74LS541, an 8-bit tri-state buffer. The clock/divider chip generates an independent clock source for the UART from the CPU clock. The UART clock must align with the baud rate, necessitating a specific frequency. The 6402 requires an input clock at 16 times the baud rate, thus a 4.9152 MHz crystal was employed. The Q6 (divide by 64) output provides 4800 baud, while the Q5 (divide by 32) output yields 9600 baud, among other rates. A jumper block has been used to facilitate baud rates of 4800, 9600, 19200, or 38400. The MAX232 chip delivers the higher voltages required for "true" RS232 signaling. Familiarity with this or similar chips (e.g., MAX202) is common among those who have worked with serial interfaces. Several electrolytic capacitors are connected to enable suitable voltage step-ups. When interfacing with TTL level USB devices, such as those based on the FT232, the level translator can be omitted, although this design intends to connect to a genuine serial port on older hardware. The tri-state buffer serves to buffer the status flags from the UART, allowing them to drive the data bus during the reading of a "status register." It is noted that the 6402 has a pin that forces the status output pins into a high impedance state when activated. While this could achieve the same function without an external chip, it also causes the Data Ready flag to enter a high impedance state. To enable this flag as an interrupt input to the Z80, continuous driving of all status pins is necessary, hence the inclusion of the buffer. The Data Ready flag, which indicates the arrival of a new byte, can interrupt the CPU. The circuit diagram features register names that may be recognizable to those familiar with the PIC UART, as the design of the 6402 closely resembles that of the PIC's UART. However, it is important to note that there is no attempt to match the bit pattern in the status register. Configuration bits for the UART (e.g., parity type, number of stop bits) are set using a series of jumpers connected with pull-up resistors, which are grounded when the jumper is fitted. Although consideration was given to integrating these into a separate register alongside the baud rate selection, the additional chips would require considerable space and wiring. It is deemed unnecessary for the system to need software configuration of the serial port, given that it serves as the primary input/output device.

The schematic design incorporates a 6402 UART as the main communication interface, facilitating serial communication with external devices. The 74HC4060 clock divider generates the necessary clock signals, ensuring that the UART operates at the required baud rate. The crystal oscillator is chosen to provide the specific frequency needed for reliable operation. The MAX232 chip is essential for converting the TTL-level signals from the UART to RS232 levels, making it compatible with traditional serial communication standards. The use of electrolytic capacitors ensures that the voltage levels are appropriately boosted for RS232 signaling.

The tri-state buffer (74LS541) plays a critical role in managing the status signals from the UART. By allowing these signals to drive the data bus, the design ensures that the CPU can effectively monitor UART status without interference. The high impedance state feature of the 6402 is leveraged to maintain continuous signal availability, particularly for the Data Ready flag, which is crucial for interrupt-driven communication.

The jumper configuration for setting the baud rate and UART parameters enhances the flexibility of the design, allowing for easy adjustments based on the application's requirements. This design approach prioritizes simplicity and functionality, ensuring that the UART system operates efficiently while minimizing the need for extensive software configuration. Overall, the schematic represents a robust solution for integrating serial communication capabilities into the existing system architecture.The basic requirement was for some sort of output display and some sort of alpha-numeric input. So the simplest solution I could think of was a UART, attached to something with a screen and keyboard running a serial terminal. I looked at using the PIC already in the system as a UART as well, but decided that it would be better used as a fast DMA c

ontroller with all its pins allocated to that. I had a 6402 UART chip of a similar vintage to the Z80 CPU lying around so that became the core of the UART peripheral. There are three peripheral chips in the UART system, a 74HC4060 clock/divider chip, a MAX232 RS232 level shifter and a 74LS541, an 8 bit tri-state buffer.

The clock/divider chip provides an independent clock source for the UART from the CPU clock. The UART clock has to match the baud-rate so needs to be a fairly weird frequency. The 6402 needs 16 times the baud-rate as an input clock, so I`ve used a 4. 9152MHz crystal. Taking the Q6 (divide by 64) output this gives 4800 baud, the Q5 (divide by 32) output gives 9600 baud and so on. I`ve used a jumper block to allow a baud rate from the range 4800, 9600, 19200 or 38400. The MAX232 chip provides the big voltages needed for "true" RS232 signalling. If you`ve made anything with a serial interface before you`ll probably be familiar with this or a similar chip (e.

g. the MAX202). There`s a bunch of electrolytic caps attached to this to make the suitable voltage step-ups. If you`re using a TTL level USB interface e. g. an FT232 based device, you need to skip the level translator, but I`m planning on plugging this into a real serial port on some old hardware I have. The final peripheral chip is the tri-state buffer. This buffers the status flags from the UART and allows them to drive the data bus when a "status register" is read.

You may notice if you are familiar with the 6402 that there is a pin on the chip that forces the status output pins to enter a high impedance state when driven high. This would of course provide the same function without an external chip. However this also forces the Data Ready flag into a high impedance state, and I wanted to make this into an interrupt input to the Z80, which would mean all the status pins would have to be driving continuously, hence the extra buffer.

This means that the Data Ready flag, which occurs when a new byte has been received can interrupt the CPU. You may notice looking at the circuit diagram that the register names are familiar if you have used the PIC UART before, that`s because I have used it a lot and found the 6402 very closely fits the PIC`s UART design, and so used those familiar names in my design.

I haven`t attempted to match the bit pattern in the status register or anything though, so don`t assume that they really are the same. The config bits for the UART (e. g. parity type, number of stop bits etc. ) I have set with a row of jumpers wired with pull-up resistors that are shorted to ground if you fit the jumper.

I considered making them into another register along with the baud rate select, but the additional chips would have take a lot of space and wiring, and I can`t see that the system is likely to need to software configure the serial port when it is the primary input/output device. 🔗 External reference

The schematic design incorporates a 6402 UART as the main communication interface, facilitating serial communication with external devices. The 74HC4060 clock divider generates the necessary clock signals, ensuring that the UART operates at the required baud rate. The crystal oscillator is chosen to provide the specific frequency needed for reliable operation. The MAX232 chip is essential for converting the TTL-level signals from the UART to RS232 levels, making it compatible with traditional serial communication standards. The use of electrolytic capacitors ensures that the voltage levels are appropriately boosted for RS232 signaling.

The tri-state buffer (74LS541) plays a critical role in managing the status signals from the UART. By allowing these signals to drive the data bus, the design ensures that the CPU can effectively monitor UART status without interference. The high impedance state feature of the 6402 is leveraged to maintain continuous signal availability, particularly for the Data Ready flag, which is crucial for interrupt-driven communication.

The jumper configuration for setting the baud rate and UART parameters enhances the flexibility of the design, allowing for easy adjustments based on the application's requirements. This design approach prioritizes simplicity and functionality, ensuring that the UART system operates efficiently while minimizing the need for extensive software configuration. Overall, the schematic represents a robust solution for integrating serial communication capabilities into the existing system architecture.The basic requirement was for some sort of output display and some sort of alpha-numeric input. So the simplest solution I could think of was a UART, attached to something with a screen and keyboard running a serial terminal. I looked at using the PIC already in the system as a UART as well, but decided that it would be better used as a fast DMA c

ontroller with all its pins allocated to that. I had a 6402 UART chip of a similar vintage to the Z80 CPU lying around so that became the core of the UART peripheral. There are three peripheral chips in the UART system, a 74HC4060 clock/divider chip, a MAX232 RS232 level shifter and a 74LS541, an 8 bit tri-state buffer.

The clock/divider chip provides an independent clock source for the UART from the CPU clock. The UART clock has to match the baud-rate so needs to be a fairly weird frequency. The 6402 needs 16 times the baud-rate as an input clock, so I`ve used a 4. 9152MHz crystal. Taking the Q6 (divide by 64) output this gives 4800 baud, the Q5 (divide by 32) output gives 9600 baud and so on. I`ve used a jumper block to allow a baud rate from the range 4800, 9600, 19200 or 38400. The MAX232 chip provides the big voltages needed for "true" RS232 signalling. If you`ve made anything with a serial interface before you`ll probably be familiar with this or a similar chip (e.

g. the MAX202). There`s a bunch of electrolytic caps attached to this to make the suitable voltage step-ups. If you`re using a TTL level USB interface e. g. an FT232 based device, you need to skip the level translator, but I`m planning on plugging this into a real serial port on some old hardware I have. The final peripheral chip is the tri-state buffer. This buffers the status flags from the UART and allows them to drive the data bus when a "status register" is read.

You may notice if you are familiar with the 6402 that there is a pin on the chip that forces the status output pins to enter a high impedance state when driven high. This would of course provide the same function without an external chip. However this also forces the Data Ready flag into a high impedance state, and I wanted to make this into an interrupt input to the Z80, which would mean all the status pins would have to be driving continuously, hence the extra buffer.

This means that the Data Ready flag, which occurs when a new byte has been received can interrupt the CPU. You may notice looking at the circuit diagram that the register names are familiar if you have used the PIC UART before, that`s because I have used it a lot and found the 6402 very closely fits the PIC`s UART design, and so used those familiar names in my design.

I haven`t attempted to match the bit pattern in the status register or anything though, so don`t assume that they really are the same. The config bits for the UART (e. g. parity type, number of stop bits etc. ) I have set with a row of jumpers wired with pull-up resistors that are shorted to ground if you fit the jumper.

I considered making them into another register along with the baud rate select, but the additional chips would have take a lot of space and wiring, and I can`t see that the system is likely to need to software configure the serial port when it is the primary input/output device. 🔗 External reference