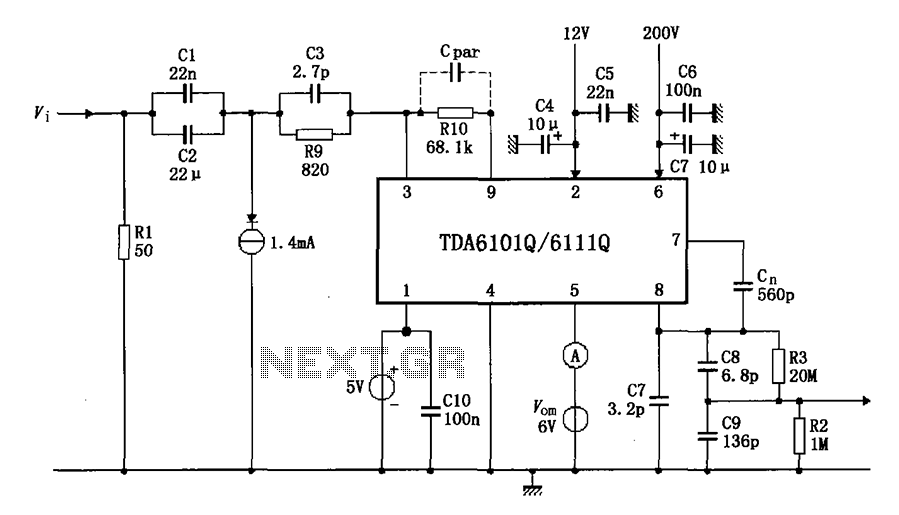

Test circuit diagram with feedback factor of 1 83 DA6101Q 6111Q

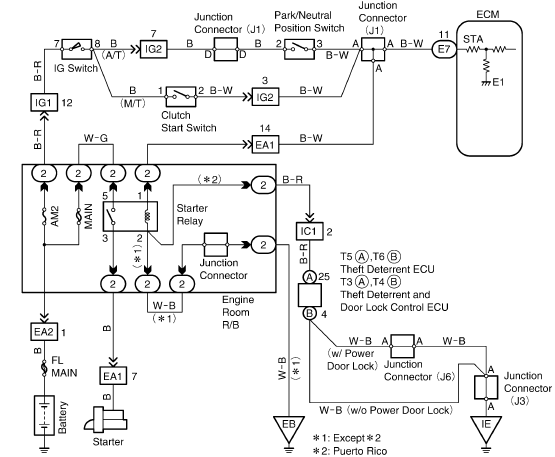

The test circuit features a feedback factor of 1/83 utilizing the DA6101Q/6111Q. The input signal is fed through a network comprising resistors R1 and R9, and capacitors C1, C2, and C3, entering the TDA6101Q, which includes three pins for the internal differential input stage at the inverting input terminal. The amplified signal is output from pin 8 and is processed through a network formed by resistors R2, R3 and capacitors C8, C9 for probing. A feedback network consisting of resistor R10 and capacitor Cpar connects between pins 3 and 9 to stabilize the current and maintain the black level automatically. Additionally, a bootstrap capacitor Cn is connected between pins 7 and 8 to enhance the dynamic range of the output. The output at pin 8 is equipped with cathode discharge protection, capable of withstanding a positive spike from a high-impedance voltage source with a maximum capacity of 100C and 5A current. In contrast, a low-impedance source can generate a positive voltage spike with a maximum capacity of 100nC and 10A current. Decoupling capacitors must be added to pins VDDH (pin 6) and VDDL (pin 2), with a recommended configuration of 20nF capacitors for high-frequency characteristics, alongside 10µF ceramic and electrolytic capacitors connected in parallel.

The DA6101Q/6111Q test circuit is designed for robust signal processing, particularly in applications requiring high fidelity and stability. The input stage utilizes a differential configuration, enhancing the common-mode rejection ratio and improving signal integrity. The feedback network comprising R10 and Cpar plays a crucial role in maintaining the black level, ensuring that the output signal remains stable regardless of variations in the input signal.

The output stage, located at pin 8, is designed to handle transient spikes effectively, offering protection against high-frequency noise and ensuring reliable operation in environments with fluctuating impedance levels. The integration of a bootstrap capacitor (Cn) between pins 7 and 8 is significant for expanding the dynamic range, allowing the circuit to handle a wider range of input signal amplitudes without distortion.

The decoupling capacitors connected to the supply pins (VDDH and VDDL) are essential for filtering out high-frequency noise that could affect the performance of the circuit. The combination of 20nF capacitors with larger 10µF capacitors ensures that the circuit remains stable during operation, particularly under varying load conditions.

Overall, this schematic design is indicative of a well-thought-out approach to signal amplification and processing, making it suitable for applications in video signal processing, high-speed data transmission, and other electronic systems requiring precise signal management. As shown for the test circuit with feedback factor of 1/83 DA6101Q/6111Q is. f input signal input through a network of R1, C1, C2, C3, R9 enter TDA6101Q composed of 3 feet, 3 f eet and 1 foot are the internal differential input stage of the inverting input terminal and inverting input terminal. The amplified signal from the 8-pin output, output through a network of R2, R3, C8, C9 formed to probe.

Between 3 feet and 9 feet resistor R10 and capacitor Cpar feedback network, from the current automatic black level stabilizing role. 8 feet and 7 feet between the resistance and capacitance Cn bootstrap capacitor, the output from the expansion of the dynamic range of action.

Output of 8 feet with a cathode discharge protection. When the high-impedance voltage source to generate a positive spike discharges can withstand 100 C largest capacity 5A current; when the low-impedance source to generate a positive voltage spike discharges can withstand 100nC maximum 10A current capacity. VDDH (6 feet), VDDL (2 feet) must be added decoupling capacitors, decoupling capacitors take 20nF good high-frequency characteristics 10 F ceramic capacitors and electrolytic capacitors connected in parallel.

The DA6101Q/6111Q test circuit is designed for robust signal processing, particularly in applications requiring high fidelity and stability. The input stage utilizes a differential configuration, enhancing the common-mode rejection ratio and improving signal integrity. The feedback network comprising R10 and Cpar plays a crucial role in maintaining the black level, ensuring that the output signal remains stable regardless of variations in the input signal.

The output stage, located at pin 8, is designed to handle transient spikes effectively, offering protection against high-frequency noise and ensuring reliable operation in environments with fluctuating impedance levels. The integration of a bootstrap capacitor (Cn) between pins 7 and 8 is significant for expanding the dynamic range, allowing the circuit to handle a wider range of input signal amplitudes without distortion.

The decoupling capacitors connected to the supply pins (VDDH and VDDL) are essential for filtering out high-frequency noise that could affect the performance of the circuit. The combination of 20nF capacitors with larger 10µF capacitors ensures that the circuit remains stable during operation, particularly under varying load conditions.

Overall, this schematic design is indicative of a well-thought-out approach to signal amplification and processing, making it suitable for applications in video signal processing, high-speed data transmission, and other electronic systems requiring precise signal management. As shown for the test circuit with feedback factor of 1/83 DA6101Q/6111Q is. f input signal input through a network of R1, C1, C2, C3, R9 enter TDA6101Q composed of 3 feet, 3 f eet and 1 foot are the internal differential input stage of the inverting input terminal and inverting input terminal. The amplified signal from the 8-pin output, output through a network of R2, R3, C8, C9 formed to probe.

Between 3 feet and 9 feet resistor R10 and capacitor Cpar feedback network, from the current automatic black level stabilizing role. 8 feet and 7 feet between the resistance and capacitance Cn bootstrap capacitor, the output from the expansion of the dynamic range of action.

Output of 8 feet with a cathode discharge protection. When the high-impedance voltage source to generate a positive spike discharges can withstand 100 C largest capacity 5A current; when the low-impedance source to generate a positive voltage spike discharges can withstand 100nC maximum 10A current capacity. VDDH (6 feet), VDDL (2 feet) must be added decoupling capacitors, decoupling capacitors take 20nF good high-frequency characteristics 10 F ceramic capacitors and electrolytic capacitors connected in parallel.