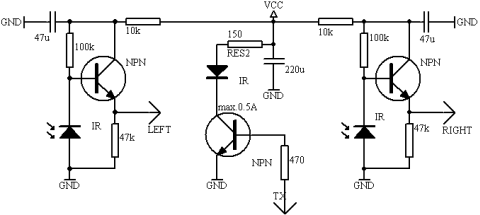

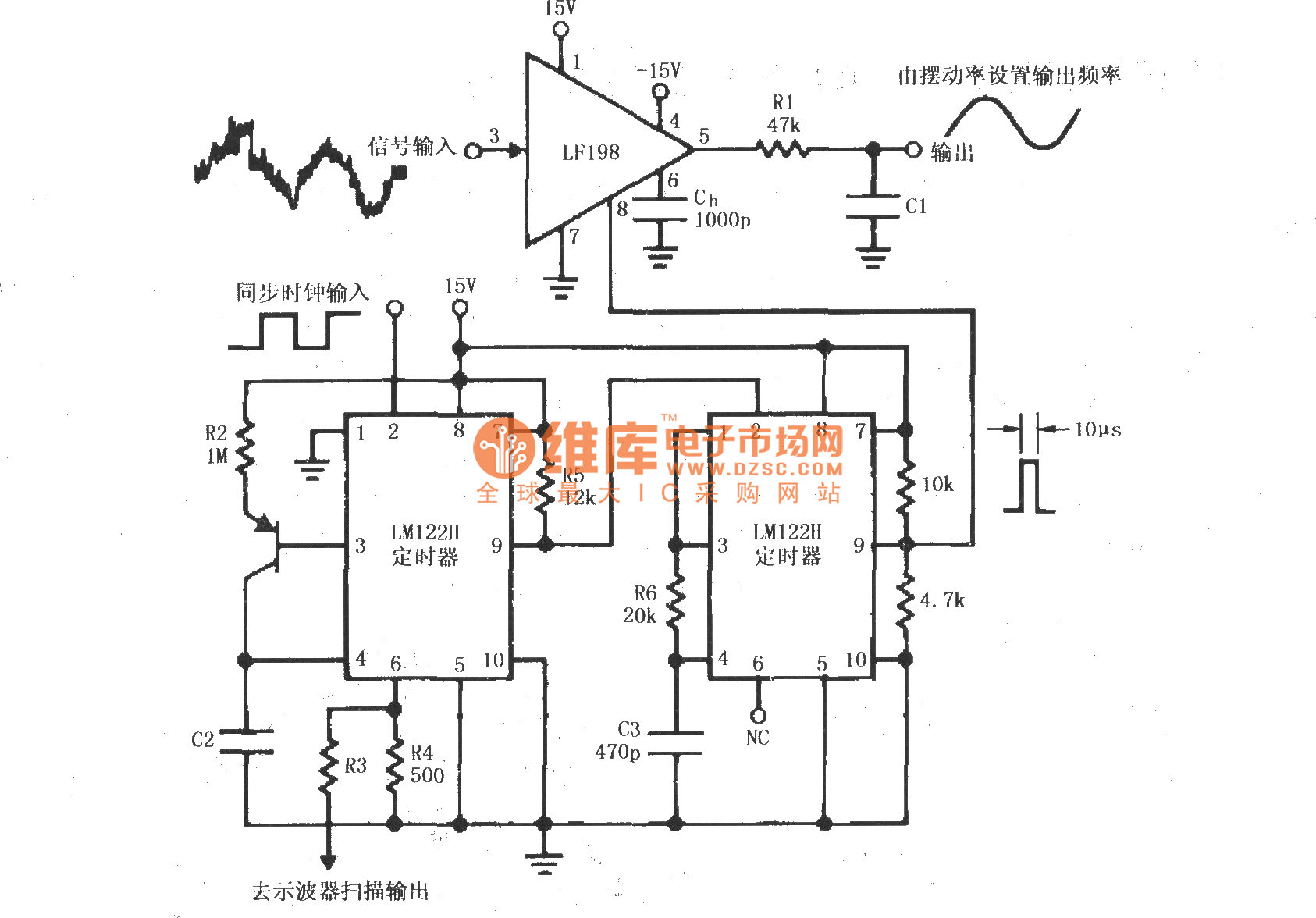

A part of product detector circuit composed of LF198 and LM122H

A synchronous clock signal is fed into a cascade of timer circuits composed of two LM122H devices. The synchronization clock is then converted into a pulse of the desired width, which is added to the LF198 logic end (pin 8) as the sampling and holding control signal. This signal is input to pin 3 of the LF198. The input signal contains a significant amount of noise.

The circuit operates by utilizing two LM122H timer ICs configured in a cascading arrangement. The first LM122H receives the synchronous clock signal and generates a pulse that is subsequently modified by the second LM122H. This configuration allows for precise control over the pulse width, which is critical for applications requiring accurate timing and synchronization.

The LF198 is a sample-and-hold amplifier that is designed to capture and hold the voltage of an input signal for a specified duration. In this setup, the output pulse from the LM122H timers serves as the control signal for the LF198, dictating when the device samples the input signal. The control signal is connected to pin 8 of the LF198, enabling the device to operate effectively in a sampling mode.

It is important to note that the input signal presented to the LF198 at pin 3 may contain various noise components. This noise can adversely affect the performance of the sample-and-hold circuit, potentially leading to inaccurate voltage readings. Therefore, appropriate filtering techniques may be required to clean the input signal before it reaches the LF198. Implementing low-pass filters or other noise-reduction strategies can help ensure that the sampled signal is as clean as possible, thus improving the overall performance of the circuit.

In summary, the described circuit effectively utilizes LM122H timer ICs to generate a controlled pulse width from a synchronous clock signal, which is then used to control the sampling process of the LF198. Careful consideration of noise management is essential for optimal circuit functionality.Synchronous clock signal is input to a cascade of timer circuit composed of two LM122H, then the synchronization clock is converted to the desired width of the pulse (Fig. 10?s) which will be add to LF198 LOGIC end (8 feet) as the sampling and holding control signal. The signal is input LF198`s pin 3. The input signal contains a large number of noise com.. 🔗 External reference

The circuit operates by utilizing two LM122H timer ICs configured in a cascading arrangement. The first LM122H receives the synchronous clock signal and generates a pulse that is subsequently modified by the second LM122H. This configuration allows for precise control over the pulse width, which is critical for applications requiring accurate timing and synchronization.

The LF198 is a sample-and-hold amplifier that is designed to capture and hold the voltage of an input signal for a specified duration. In this setup, the output pulse from the LM122H timers serves as the control signal for the LF198, dictating when the device samples the input signal. The control signal is connected to pin 8 of the LF198, enabling the device to operate effectively in a sampling mode.

It is important to note that the input signal presented to the LF198 at pin 3 may contain various noise components. This noise can adversely affect the performance of the sample-and-hold circuit, potentially leading to inaccurate voltage readings. Therefore, appropriate filtering techniques may be required to clean the input signal before it reaches the LF198. Implementing low-pass filters or other noise-reduction strategies can help ensure that the sampled signal is as clean as possible, thus improving the overall performance of the circuit.

In summary, the described circuit effectively utilizes LM122H timer ICs to generate a controlled pulse width from a synchronous clock signal, which is then used to control the sampling process of the LF198. Careful consideration of noise management is essential for optimal circuit functionality.Synchronous clock signal is input to a cascade of timer circuit composed of two LM122H, then the synchronization clock is converted to the desired width of the pulse (Fig. 10?s) which will be add to LF198 LOGIC end (8 feet) as the sampling and holding control signal. The signal is input LF198`s pin 3. The input signal contains a large number of noise com.. 🔗 External reference

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713