A user friendly boost DC DC converter topology

In battery-powered applications such as cell phones, PDAs, and digital cameras, an integrated DC-DC converter circuit solution provides multiple advantages regarding cost, size, and design complexity. A significant challenge in achieving a fully integrated solution is designing the frequency compensation circuit, which must be tailored based on the values of external passive filter components (L-C) and their associated parasitic elements, including the capacitor's equivalent series resistance (ESR). The values of these off-chip components can vary due to manufacturing tolerances, parameter drift, and design requirements. Capacitor ESR can differ significantly, depending on whether the capacitor is electrolytic or ceramic, and can also vary with temperature. Therefore, a DC-DC controller IC is necessary to ensure rapid control and stable operation with a wide range of varying passive component values. In hysteretic control for buck converters, the regulated output voltage incorporates inductor current ripple information sensed indirectly through capacitor ESR, which simplifies the loop characteristics. This circuit exhibits inherently stable performance, and any changes in L-C values are managed by adjusting the converter's switching frequency, thereby maintaining stable operation without the need for frequency compensation circuits. However, in boost converters, which are utilized to step up single or dual-cell battery voltages for 3.3V or 5V applications, this technique is not directly applicable because the inductor current cannot be fully determined from the output voltage. A method to address this limitation in boost converters involves independently sensing and regulating the inductor current through a separate hysteretic loop that includes the main switch (SM). The average inductor current (IL) is maintained above the minimum required value to support the load current (IO). In a standard boost converter, an additional auxiliary switch (SA) is placed across the inductor (L). When switch SA is open, excess inductor current (above the minimum value) can charge the capacitor (C) beyond the desired output voltage. This overcharge is detected and prevented by a comparator (Q1), which activates switch SA, shorting the inductor L. Consequently, the inductor current freewheels, turning off diode D and allowing the capacitor voltage to discharge. Switch SA is deactivated when the sensed capacitor voltage (VS) falls below the reference voltage (VREF). The hysteretic problem is thus defined to regulate the output voltage to a target value between (VIN - VDiode), which represents its equilibrium state with switch SA closed, and ID(VOUT/IO), which corresponds to its equilibrium state with switch SA open. This regulation is achieved by adjusting the duty cycle (DA) of switch SA. At the correct duty cycle DA, the diode current (ID), averaged over a switching cycle of SA, equals the load current (IO), stabilizing the average output voltage (VOUT) to equal VREF. Switch SA operates asynchronously to switch SM at a significantly lower switching frequency. The additional power loss from the increased inductor current is minimized by keeping the inductor current only 5% above the minimum required value (IL_Min). A representative inductor current reference (VIREF) is derived from the duty cycle DA through a charge-pump-based duty-cycle-to-voltage demodulator. Capacitor C1 is charged and discharged by complementary switching current sources (I1 and I2), which are controlled by the signal for switch SA. The average capacitor current is zero, and the voltage VIREF stabilizes when the total charge injected into the capacitor by I1 during the off time of switch SA equals the total charge removed by I2 during the on time of switch SA. By setting I2 to be 19 times larger than I1, VIREF reaches a steady state only when the off time of switch SA is appropriately managed.

In designing a DC-DC converter for battery-powered applications, the integration of a frequency compensation circuit is critical for ensuring stable operation across varying load conditions and component tolerances. The use of hysteretic control in buck converters simplifies the feedback loop by leveraging the inductor current ripple information sensed through the capacitor ESR, which inherently stabilizes the output. This approach allows for a responsive adjustment of the switching frequency to accommodate changes in the passive components without the need for complex compensation networks.

For applications requiring voltage step-up, the boost converter architecture presents unique challenges in current sensing and regulation. The implementation of an auxiliary switch (SA) and a separate hysteretic control loop enables precise management of inductor current, ensuring that it remains above the minimum threshold to support load demands. This method enhances the converter's performance by preventing overcharging while maintaining efficiency through asynchronous switching. The design also considers the trade-offs associated with increased inductor current, ensuring that power losses are kept within acceptable limits.

The charge-pump-based duty-cycle-to-voltage demodulator further enhances the control strategy by providing a reliable reference for inductor current regulation. By balancing the charge injected and removed from capacitor C1, the system can maintain a stable voltage reference (VIREF), crucial for the effective operation of the boost converter. Overall, the integration of these techniques results in a robust DC-DC converter solution suitable for a variety of battery-powered devices, optimizing both performance and efficiency.In battery-powered applications, like cell phones, PDAs, digital cameras, etc. , an integrated dc-dc converter circuit solution offers several advantages in terms of cost, size, and design complexity. A critical hurdle in obtaining a fully integrated solution is the frequency compensation circuit, which has to be designed based on the values of external passive filter components

(L-C) and associated parasitic elements, like the capacitor equivalent series resistance (ESR). The values of these off-chip components vary due to manufacturing tolerances, parameter drift, and design requirements. Capacitor ESR can vary by orders of magnitude, based on whether the capacitor is electrolytic or ceramic, not to mention its variation across temperature.

As such, it is required to have a DC-DC controller IC that can provide fast control and stable operation with widely varying passive component values. In hysteretic control for buck converters, the regulated output voltage includes inductor current ripple information sensed indirectly through capacitor ESR, thus simplifying the loop characteristics.

This circuit displays an inherently stable performance and any change in L-C values is accommodated through a change in the converter switching frequency, maintaining stable operation without the use of frequency compensation circuits [1-2]. However, in boost converters, which are used for stepping up single or dual-cell battery voltages for 3.

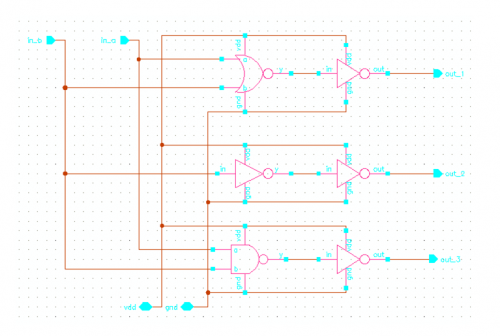

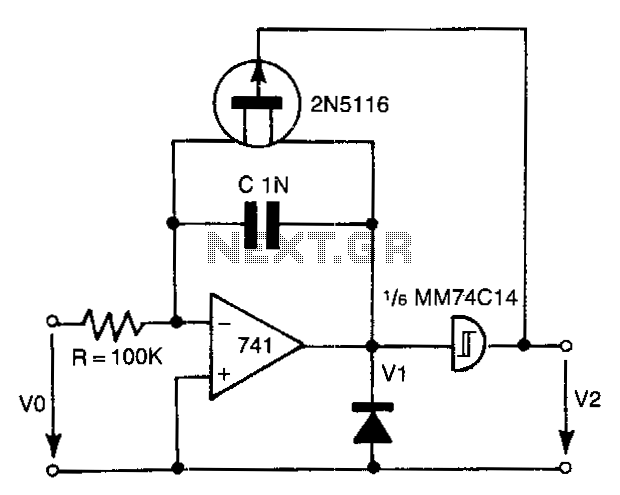

3 or 5 V applications, the technique is not readily applicable because the inductor current cannot be determined entirely from the output voltage. A strategy that overcomes this limitation in boost converters is presented in Figure 1 [3]. The inductor current, which cannot be determined completely through the capacitor voltage ripple, is independently sensed and regulated through a separate hysteretic loop, containing the main switch SM.

The average inductor current IL is raised above the minimum value required to support load current IO. Starting with a standard boost converter, an additional auxiliary switch SA is added across the inductor L.

When the switch SA is open, the excess inductor current (above the minimum value) tends to charge the capacitor C beyond the desired output voltage. This overcharge is sensed and prevented by comparator Q1, which turns on switch SA and shorts inductor L.

Therefore, the inductor current freewheels, shutting off diode D and letting the capacitor voltage discharge. Switch SA is turned back off when the sensed capacitor voltage VS discharges below reference VREF. The hysteretic problem is thus defined to regulate the output voltage to a desired value between (VIN - VDiode), which is its equilibrium value with switch SA closed, and ID(VOUT/IO), which is its equilibrium value with switch SA open.

This regulation is performed by controlling the duty cycle DA of switch SA. At the appropriate duty cycle DA, the diode current ID, averaged over a switching cycle of SA, equals the load current IO, and average VOUT is stabilized to equal VREF. Switch SA switches asynchronously to switch SM at a much lower switching frequency. The additional power loss due to higher inductor current is kept low by maintaining the inductor current only 5% above the minimum required value (IL_Min).

A representative inductor current reference (VIREF) is derived from duty cycle DA, by means of a charge-pump-based duty-cycle-to-voltage demodulator shown in Fig. 1b. Capacitor C1 is charged and discharged by complementarily switching current sources I1 and I2, which are gated by the controlling signal of switch SA.

The average capacitor current equals zero and the voltage VIREF stabilizes when the total charge injected into the capacitor by I1 during the off time of switch SA balances the total charge removed by I2 during the on time of switch SA. By setting I2 to be 19 times larger than I1, VIREF reaches steady state only when the off t 🔗 External reference

In designing a DC-DC converter for battery-powered applications, the integration of a frequency compensation circuit is critical for ensuring stable operation across varying load conditions and component tolerances. The use of hysteretic control in buck converters simplifies the feedback loop by leveraging the inductor current ripple information sensed through the capacitor ESR, which inherently stabilizes the output. This approach allows for a responsive adjustment of the switching frequency to accommodate changes in the passive components without the need for complex compensation networks.

For applications requiring voltage step-up, the boost converter architecture presents unique challenges in current sensing and regulation. The implementation of an auxiliary switch (SA) and a separate hysteretic control loop enables precise management of inductor current, ensuring that it remains above the minimum threshold to support load demands. This method enhances the converter's performance by preventing overcharging while maintaining efficiency through asynchronous switching. The design also considers the trade-offs associated with increased inductor current, ensuring that power losses are kept within acceptable limits.

The charge-pump-based duty-cycle-to-voltage demodulator further enhances the control strategy by providing a reliable reference for inductor current regulation. By balancing the charge injected and removed from capacitor C1, the system can maintain a stable voltage reference (VIREF), crucial for the effective operation of the boost converter. Overall, the integration of these techniques results in a robust DC-DC converter solution suitable for a variety of battery-powered devices, optimizing both performance and efficiency.In battery-powered applications, like cell phones, PDAs, digital cameras, etc. , an integrated dc-dc converter circuit solution offers several advantages in terms of cost, size, and design complexity. A critical hurdle in obtaining a fully integrated solution is the frequency compensation circuit, which has to be designed based on the values of external passive filter components

(L-C) and associated parasitic elements, like the capacitor equivalent series resistance (ESR). The values of these off-chip components vary due to manufacturing tolerances, parameter drift, and design requirements. Capacitor ESR can vary by orders of magnitude, based on whether the capacitor is electrolytic or ceramic, not to mention its variation across temperature.

As such, it is required to have a DC-DC controller IC that can provide fast control and stable operation with widely varying passive component values. In hysteretic control for buck converters, the regulated output voltage includes inductor current ripple information sensed indirectly through capacitor ESR, thus simplifying the loop characteristics.

This circuit displays an inherently stable performance and any change in L-C values is accommodated through a change in the converter switching frequency, maintaining stable operation without the use of frequency compensation circuits [1-2]. However, in boost converters, which are used for stepping up single or dual-cell battery voltages for 3.

3 or 5 V applications, the technique is not readily applicable because the inductor current cannot be determined entirely from the output voltage. A strategy that overcomes this limitation in boost converters is presented in Figure 1 [3]. The inductor current, which cannot be determined completely through the capacitor voltage ripple, is independently sensed and regulated through a separate hysteretic loop, containing the main switch SM.

The average inductor current IL is raised above the minimum value required to support load current IO. Starting with a standard boost converter, an additional auxiliary switch SA is added across the inductor L.

When the switch SA is open, the excess inductor current (above the minimum value) tends to charge the capacitor C beyond the desired output voltage. This overcharge is sensed and prevented by comparator Q1, which turns on switch SA and shorts inductor L.

Therefore, the inductor current freewheels, shutting off diode D and letting the capacitor voltage discharge. Switch SA is turned back off when the sensed capacitor voltage VS discharges below reference VREF. The hysteretic problem is thus defined to regulate the output voltage to a desired value between (VIN - VDiode), which is its equilibrium value with switch SA closed, and ID(VOUT/IO), which is its equilibrium value with switch SA open.

This regulation is performed by controlling the duty cycle DA of switch SA. At the appropriate duty cycle DA, the diode current ID, averaged over a switching cycle of SA, equals the load current IO, and average VOUT is stabilized to equal VREF. Switch SA switches asynchronously to switch SM at a much lower switching frequency. The additional power loss due to higher inductor current is kept low by maintaining the inductor current only 5% above the minimum required value (IL_Min).

A representative inductor current reference (VIREF) is derived from duty cycle DA, by means of a charge-pump-based duty-cycle-to-voltage demodulator shown in Fig. 1b. Capacitor C1 is charged and discharged by complementarily switching current sources I1 and I2, which are gated by the controlling signal of switch SA.

The average capacitor current equals zero and the voltage VIREF stabilizes when the total charge injected into the capacitor by I1 during the off time of switch SA balances the total charge removed by I2 during the on time of switch SA. By setting I2 to be 19 times larger than I1, VIREF reaches steady state only when the off t 🔗 External reference