Alarm Dialer Circuit

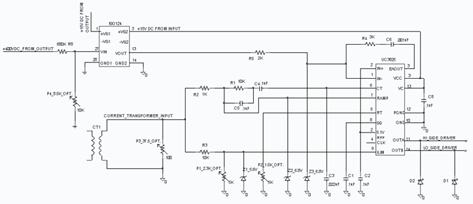

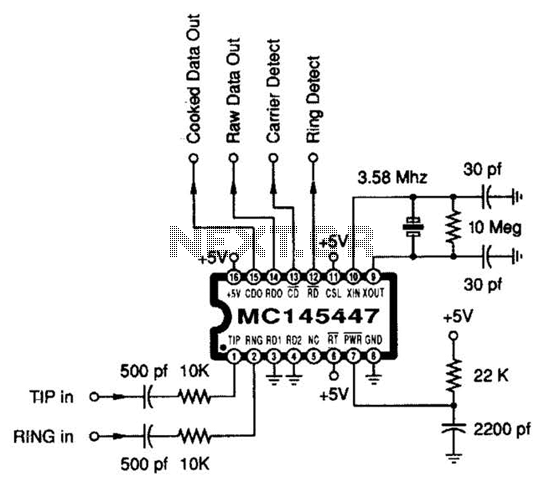

This circuit dials a stored DTMF tone sequence from an EPROM when a control line is taken to 0 V. IC1 is a Schmitt trigger oscillator, operating at approximately 2 Hz. It clocks a 4024 binary counter. The outputs of the counter connect to the address leads of the EPROM. A 2716 EPROM is utilized in this design, but the specific choice of EPROM is not critical. Normally, the counter is held in a reset state by a logic high on its reset pin (pin 2). When the trigger input is set low, pin 10 of IC1 goes low, pin 3 goes high, and the reset condition is removed from the counter, allowing it to start clocking and incrementing the EPROM. When the address moves from 000000, the data on bit D0 of the EPROM changes to a logic high, maintaining the circuit operation. The final address should contain data 11111110 to reset the circuit to standby.

The described circuit operates on the principle of generating Dual-Tone Multi-Frequency (DTMF) signals using an EPROM and a binary counter. The core component, IC1, functions as a Schmitt trigger oscillator, which provides a stable square wave output at a frequency of approximately 2 Hz. This output is used to clock the 4024 binary counter, which counts in binary and thus produces a sequence of binary outputs corresponding to its count.

The outputs of the 4024 counter are connected to the address lines of the EPROM, specifically the 2716 model in this example. The 2716 EPROM is a 2K x 8 memory device, capable of storing a sequence of DTMF tones. The counter's output determines the address being accessed in the EPROM, effectively allowing the circuit to sequentially read the stored DTMF tone data.

In normal operation, the counter is held in a reset state by applying a logic high to its reset pin (pin 2). This prevents any counting from occurring until a trigger input is applied. When the control line is driven low, the circuit initiates its operation: pin 10 of IC1 transitions to a low state, which in turn causes pin 3 to go high, removing the reset condition from the counter. With the reset condition lifted, the counter begins to increment with each clock pulse from the Schmitt trigger oscillator, sequentially addressing the EPROM.

As the counter progresses through its counts, the EPROM outputs the corresponding DTMF tone data. The data on the least significant bit (D0) of the EPROM serves a critical role; when the address changes from 000000, D0 transitions to a logic high, which keeps the circuit operational. To ensure the circuit can return to a standby state, the last address accessed in the EPROM must contain the data pattern 11111110. This specific data instructs the circuit to reset, preparing it for the next operation cycle.

Overall, this circuit effectively demonstrates the use of a binary counter and an EPROM to generate and control a sequence of DTMF tones, showcasing a practical application of digital electronics in communication systems. This circuit dials a stored DTMF tone sequence from EPROM when a control line is taken to 0 V. ICl is a Schmitt trigger oscillator, running at around 2 Hz. It clocks a 4024 binary counter. The counter`s outputs connect to the address leads of the EPROM. A 2716 was used here, but the choice of EPROM is by no means critical. Normally, the counter is held reset by a logic 1 on its reset pin (pin 2). When the trigger input is sent low, pin 10 of ICl goes low, pin 3 goes high, and the reset is removed from the counter. It then begins to clock, incrementing the EPROM. When moved from address 000000, the data on bit DO of the EPROM changes to a logic 1 and holds the circuit running. The last address should have data 11111110 to reset the circuit to standby.

The described circuit operates on the principle of generating Dual-Tone Multi-Frequency (DTMF) signals using an EPROM and a binary counter. The core component, IC1, functions as a Schmitt trigger oscillator, which provides a stable square wave output at a frequency of approximately 2 Hz. This output is used to clock the 4024 binary counter, which counts in binary and thus produces a sequence of binary outputs corresponding to its count.

The outputs of the 4024 counter are connected to the address lines of the EPROM, specifically the 2716 model in this example. The 2716 EPROM is a 2K x 8 memory device, capable of storing a sequence of DTMF tones. The counter's output determines the address being accessed in the EPROM, effectively allowing the circuit to sequentially read the stored DTMF tone data.

In normal operation, the counter is held in a reset state by applying a logic high to its reset pin (pin 2). This prevents any counting from occurring until a trigger input is applied. When the control line is driven low, the circuit initiates its operation: pin 10 of IC1 transitions to a low state, which in turn causes pin 3 to go high, removing the reset condition from the counter. With the reset condition lifted, the counter begins to increment with each clock pulse from the Schmitt trigger oscillator, sequentially addressing the EPROM.

As the counter progresses through its counts, the EPROM outputs the corresponding DTMF tone data. The data on the least significant bit (D0) of the EPROM serves a critical role; when the address changes from 000000, D0 transitions to a logic high, which keeps the circuit operational. To ensure the circuit can return to a standby state, the last address accessed in the EPROM must contain the data pattern 11111110. This specific data instructs the circuit to reset, preparing it for the next operation cycle.

Overall, this circuit effectively demonstrates the use of a binary counter and an EPROM to generate and control a sequence of DTMF tones, showcasing a practical application of digital electronics in communication systems. This circuit dials a stored DTMF tone sequence from EPROM when a control line is taken to 0 V. ICl is a Schmitt trigger oscillator, running at around 2 Hz. It clocks a 4024 binary counter. The counter`s outputs connect to the address leads of the EPROM. A 2716 was used here, but the choice of EPROM is by no means critical. Normally, the counter is held reset by a logic 1 on its reset pin (pin 2). When the trigger input is sent low, pin 10 of ICl goes low, pin 3 goes high, and the reset is removed from the counter. It then begins to clock, incrementing the EPROM. When moved from address 000000, the data on bit DO of the EPROM changes to a logic 1 and holds the circuit running. The last address should have data 11111110 to reset the circuit to standby.