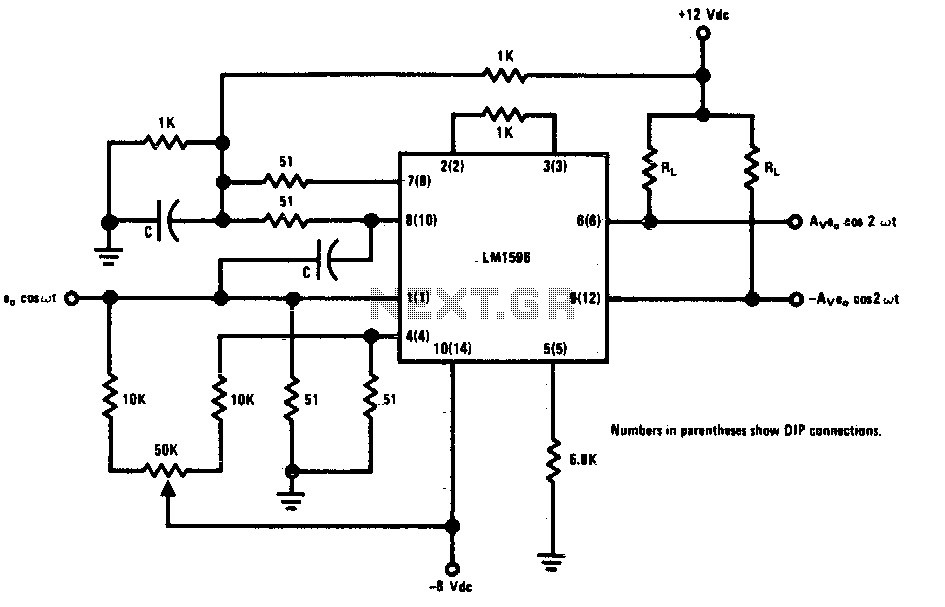

Broadband frequency doubler

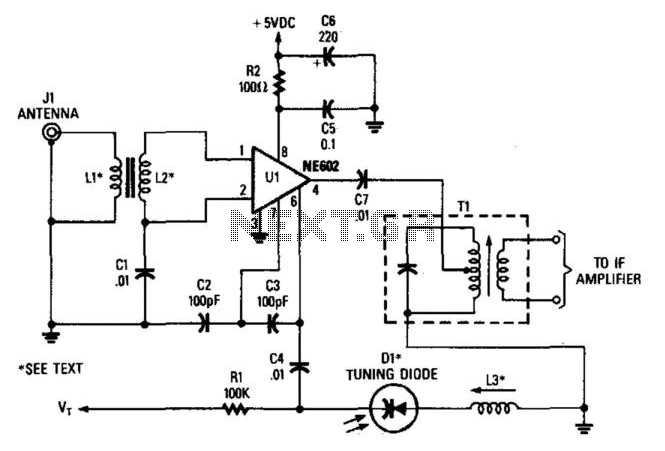

This circuit is designed to double low-level signals while maintaining low distortion. The capacitor value (C) should be selected to ensure low reactance at the operating frequency. The signal level at the carrier input should remain below 25 mV peak to ensure operation within the linear region of the switching differential amplifier. Input levels up to 50 mV peak may be utilized, but this may introduce some distortion in the output waveform. Additionally, if a higher input signal is accessible, a resistive divider can be implemented at the carrier input, allowing the full signal to be fed into the signal input.

This circuit employs a switching differential amplifier configuration to achieve signal doubling. The amplifier operates in a linear region when the input signal at the carrier input is maintained below 25 mV peak, ensuring minimal distortion in the output. The selection of capacitor C is crucial; it should be chosen based on the operating frequency of the circuit to minimize reactance, thereby optimizing performance.

In scenarios where higher input signals are present, the use of a resistive divider is recommended. This technique allows for the attenuation of the input signal to a level suitable for the carrier input while enabling the full input signal to be utilized at the signal input. The resistive divider should be carefully designed to ensure that the voltage drop across the divider does not exceed the specified threshold for linear operation.

The output waveform integrity is paramount, and while levels approaching 50 mV peak can be accommodated, the resultant distortion must be assessed based on the application's requirements. It is essential to balance the input signal levels and the desired output fidelity to achieve optimal circuit performance.This circuit will double low-level signals with low distortion. The value of C should be chosen for low reactance at the operating frequency. Signal level at the carrier input must be less than 25 mV peak to maintain operation in the linear region of the switching differential amplifier. Levels to 50 mV peak may be used with some distortion of the output waveform If a larger input signal is available, a resistive divider may be used at the carrier input with full signal applied to the signal input. 🔗 External reference

This circuit employs a switching differential amplifier configuration to achieve signal doubling. The amplifier operates in a linear region when the input signal at the carrier input is maintained below 25 mV peak, ensuring minimal distortion in the output. The selection of capacitor C is crucial; it should be chosen based on the operating frequency of the circuit to minimize reactance, thereby optimizing performance.

In scenarios where higher input signals are present, the use of a resistive divider is recommended. This technique allows for the attenuation of the input signal to a level suitable for the carrier input while enabling the full input signal to be utilized at the signal input. The resistive divider should be carefully designed to ensure that the voltage drop across the divider does not exceed the specified threshold for linear operation.

The output waveform integrity is paramount, and while levels approaching 50 mV peak can be accommodated, the resultant distortion must be assessed based on the application's requirements. It is essential to balance the input signal levels and the desired output fidelity to achieve optimal circuit performance.This circuit will double low-level signals with low distortion. The value of C should be chosen for low reactance at the operating frequency. Signal level at the carrier input must be less than 25 mV peak to maintain operation in the linear region of the switching differential amplifier. Levels to 50 mV peak may be used with some distortion of the output waveform If a larger input signal is available, a resistive divider may be used at the carrier input with full signal applied to the signal input. 🔗 External reference