current mode amp powers 24 ghz

It is possible to apply switch-mode techniques to a silicon CMOS semiconductor process to create a current-mode power amplifier with high gain and efficiency for use in 2.4-GHz wireless applications. Amplification at 2.4 GHz is essential for various wireless applications, and CMOS provides a cost-effective and efficient method for achieving significant gain at this frequency. To support wireless transmitters at 2.4 GHz, a CMOS current-mode power amplifier was developed to enhance efficiency. This amplifier comprises two differential amplifier stages. The first stage is a driver derived from current mirrors, while the second stage functions as a current-mode Class D amplifier. All components, including inductors, are integrated on the CMOS chip. Simulations conducted with a commercial computer-aided-engineering (CAE) software package from Cadence Design Systems show a high power-added efficiency (PAE) of 40% with a 0.25-W saturated output power and substantial gain while operating at a 3.3-VDC supply. The rapid proliferation of wireless devices and services has increased the demand for practical solid-state devices, including amplifiers. Many applications are being addressed by single-chip radios, with several RF front-end functions, such as the low-noise amplifier (LNA), frequency mixer, and voltage-controlled oscillator (VCO) serving as the radio's local oscillator (LO), integrated onto a single chip using silicon CMOS processes. However, certain limitations of CMOS technology—such as thermal dissipation, power efficiency, and supply voltage—have hindered the integration of the power amplifier (PA) output stage. The PA is a crucial component of a 2.4-GHz wireless radio, supporting the transmitter section. PA performance can be evaluated using several parameters, including output power, gain, and efficiency, with efficiency being particularly important for extended battery life. High efficiency also leads to reduced heat generation in the output circuitry. Various topologies have been employed for RF PAs, differentiated by the operational states of the active devices (transistors). For instance, different classes of linear PAs—Classes A, B, and C—utilize a constant power supply to energize the transistors. In contrast, switched-mode PAs—Classes D, E, and F—turn the power supplies on and off. Each type of PA has its advantages and disadvantages: linear amplifiers provide good linearity but are less efficient, while switched-mode amplifiers prioritize efficiency over linearity. Class D switched-mode amplifiers have typically been used for low-frequency applications, but their use at higher frequencies is limited due to excessive parasitic capacitance discharge losses. However, a modified Class D architecture, known as a current-mode Class D (CMCD) PA, employs zero voltage switching (ZVS) to minimize discharge losses and can operate at higher frequencies. Most current-mode Class D PAs have been fabricated using gallium arsenide (GaAs) field-effect transistors (FETs) or silicon lateral diffused metal-oxide-semiconductor (LDMOS) FETs, which restricts their fabrication as silicon CMOS chips. A two-stage amplifier has been designed for high efficiency using a silicon CMOS process. The first driver stage accepts input current signals and amplifies them into larger driving signals for the subsequent stage. The second stage primarily acts as the PA. Spiral inductors have been utilized to facilitate the use of on-chip inductors. For analysis, the amplifier design was simulated using the Cadence Spectre CAE program for a CHRT 0.18-µm mixed-signal/RF CMOS process. The simulations indicated that this PA design achieves higher efficiency and output power than other CMOS PAs operating at the same frequency.

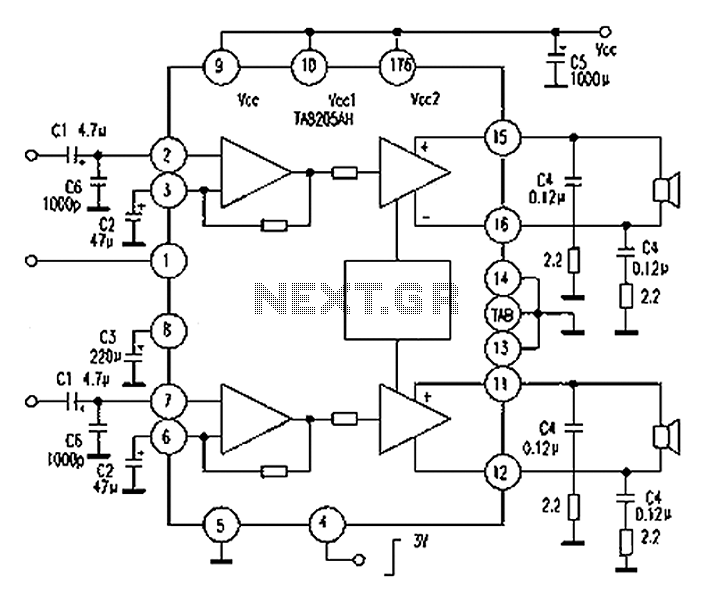

The circuit design for this high-efficiency CMOS power amplifier features a two-stage configuration that optimizes performance for 2.4-GHz applications. The first stage, a differential driver, utilizes current mirrors to ensure precise current amplification while maintaining low power consumption. The driver stage is crucial for preparing the input signal for the subsequent amplification stage, effectively boosting the signal strength without introducing significant distortion.

The second stage employs a current-mode Class D amplifier, which is characterized by its ability to switch the output devices rapidly, thus maximizing efficiency and minimizing heat generation. This stage is designed to operate under zero voltage switching conditions, which significantly reduces switching losses and enhances overall power efficiency. The integration of spiral inductors on the CMOS chip allows for compact design while maintaining the necessary inductive elements for proper operation at high frequencies.

Simulation results indicate that the amplifier achieves a power-added efficiency of 40% at a supply voltage of 3.3 V, with a saturated output power of 0.25 W. These parameters demonstrate the effectiveness of the CMOS technology in achieving high-performance amplification suitable for modern wireless communication applications. The use of a mixed-signal/RF CMOS process further supports the integration of additional RF front-end components, contributing to the development of compact, single-chip solutions for wireless transmitters. The design and simulation methodologies employed ensure that the amplifier meets the rigorous demands of efficiency, output power, and gain, positioning it as a viable option for 2.4-GHz wireless applications.It is possible to apply switch-mode approaches to a silicon CMOS semiconductor process to fabricate a current-mode power amplifier with high gain and efficiency for use in 2. 4-GHz wireless applications. Amplification at 2. 4 GHz is necessary for a number of different wireless applications, and CMOS offers a low-cost and effective process for achieving respectable gain at that frequency.

In support of wireless transmitters at 2. 4 GHz, a 2. 4-GHz CMOS current-mode power amplifier was developed for improved efficiency. It consists of two differential amplifier stages. The first stage is a driver evolved from current mirrors, while the second stage is a current-mode Class D amplifier. All components, including the inductors, are on the CMOS chip. Simulations performed with a commercial computer-aided-engineering (CAE) software package (from Cadence Design Systems ) indicate high power-added efficiency (PAE) of 40% with 0.

25-W saturated output power and high gain when operating at a 3. 3-VDC supply. The rapid growth of wireless devices and services has driven the need for practical solid-state devices, including amplifiers. Many applications are being served by single-chip radios. 1 Many of the RF front-end functions, such as the low-noise amplifier (LNA), frequency mixer, and voltage-controlled oscillator (VCO) serving as the radio`s local oscillator (LO) have been integrated onto a single chip using silicon CMOS processes.

But some of the limitations of CMOS technology ”such as thermal dissipation, power efficiency, and supply voltage ”have prevented the integration of the power amplifier (PA) output stage. 2 Of course, the PA is a key part of a 2. 4-GHz wireless radio, supporting the transmitter section. PA performance can be judged by a number of parameters, including output power, gain, and efficiency, with one of the more important characteristics (especially for extended battery life) being the efficiency.

3 High efficiency can also translate into less heat produced by the output circuitry. A number of different topologies have been applied for RF PAs, differentiated by the operational states of the active devices (transistors). For example, different classes of linear PAs ”including Classes A, B, and C ”refer to the use of a constant power supply in energizing the transistors.

In contrast, switched-mode PAs ” such as Classes D, E, and F ”turn the power supplies on and off. 4 Each of these types of PA have advantages and disadvantages: Linear amplifiers offer good linearity at the expense of efficiency, while switched-mode amplifiers sacrifice linearity for efficiency. Class D switched-mode amplifiers have often been used for low-frequency applications, but less so at higher frequencies.

At the latter frequencies, the parasitic capacitance discharge losses become excessive. But a modified Class D structure, known as a current-mode Class D (CMCD) PA uses zero voltage switching (ZVS) to minimize discharge losses and can work at higher frequencies. 5-8 Most current-mode Class D PAs have been fabricated with gallium arsenide (GaAs) field-effect transistors (FETs)5, 6 or silicon lateral diffused metal-oxide-semiconductor (LDMO) FETs.

7, 8 The use of these technologies prevents fabrication as a silicon CMOS chip. A two-stage amplifier was designed for high efficiency in a silicon CMOS process. The first, driver stage accepts input current signals and converts them to larger driving signals for the following stage. The second stage is basically a PA. Spiral inductors were used to allow the use of on-chip inductors. For analysis, the amplifier design was simulated using the Cadence Spectre ® CAE program for a CHRT 0.

18- m mixed-signal/RF CMOS process. The simulations revealed that this PA design offers higher efficiency and output power than other CMOS PAs working at the same frequency. 9-13 Figure 1 presents the circuit for this high-efficiency CMOS PA. The driver 🔗 External reference

The circuit design for this high-efficiency CMOS power amplifier features a two-stage configuration that optimizes performance for 2.4-GHz applications. The first stage, a differential driver, utilizes current mirrors to ensure precise current amplification while maintaining low power consumption. The driver stage is crucial for preparing the input signal for the subsequent amplification stage, effectively boosting the signal strength without introducing significant distortion.

The second stage employs a current-mode Class D amplifier, which is characterized by its ability to switch the output devices rapidly, thus maximizing efficiency and minimizing heat generation. This stage is designed to operate under zero voltage switching conditions, which significantly reduces switching losses and enhances overall power efficiency. The integration of spiral inductors on the CMOS chip allows for compact design while maintaining the necessary inductive elements for proper operation at high frequencies.

Simulation results indicate that the amplifier achieves a power-added efficiency of 40% at a supply voltage of 3.3 V, with a saturated output power of 0.25 W. These parameters demonstrate the effectiveness of the CMOS technology in achieving high-performance amplification suitable for modern wireless communication applications. The use of a mixed-signal/RF CMOS process further supports the integration of additional RF front-end components, contributing to the development of compact, single-chip solutions for wireless transmitters. The design and simulation methodologies employed ensure that the amplifier meets the rigorous demands of efficiency, output power, and gain, positioning it as a viable option for 2.4-GHz wireless applications.It is possible to apply switch-mode approaches to a silicon CMOS semiconductor process to fabricate a current-mode power amplifier with high gain and efficiency for use in 2. 4-GHz wireless applications. Amplification at 2. 4 GHz is necessary for a number of different wireless applications, and CMOS offers a low-cost and effective process for achieving respectable gain at that frequency.

In support of wireless transmitters at 2. 4 GHz, a 2. 4-GHz CMOS current-mode power amplifier was developed for improved efficiency. It consists of two differential amplifier stages. The first stage is a driver evolved from current mirrors, while the second stage is a current-mode Class D amplifier. All components, including the inductors, are on the CMOS chip. Simulations performed with a commercial computer-aided-engineering (CAE) software package (from Cadence Design Systems ) indicate high power-added efficiency (PAE) of 40% with 0.

25-W saturated output power and high gain when operating at a 3. 3-VDC supply. The rapid growth of wireless devices and services has driven the need for practical solid-state devices, including amplifiers. Many applications are being served by single-chip radios. 1 Many of the RF front-end functions, such as the low-noise amplifier (LNA), frequency mixer, and voltage-controlled oscillator (VCO) serving as the radio`s local oscillator (LO) have been integrated onto a single chip using silicon CMOS processes.

But some of the limitations of CMOS technology ”such as thermal dissipation, power efficiency, and supply voltage ”have prevented the integration of the power amplifier (PA) output stage. 2 Of course, the PA is a key part of a 2. 4-GHz wireless radio, supporting the transmitter section. PA performance can be judged by a number of parameters, including output power, gain, and efficiency, with one of the more important characteristics (especially for extended battery life) being the efficiency.

3 High efficiency can also translate into less heat produced by the output circuitry. A number of different topologies have been applied for RF PAs, differentiated by the operational states of the active devices (transistors). For example, different classes of linear PAs ”including Classes A, B, and C ”refer to the use of a constant power supply in energizing the transistors.

In contrast, switched-mode PAs ” such as Classes D, E, and F ”turn the power supplies on and off. 4 Each of these types of PA have advantages and disadvantages: Linear amplifiers offer good linearity at the expense of efficiency, while switched-mode amplifiers sacrifice linearity for efficiency. Class D switched-mode amplifiers have often been used for low-frequency applications, but less so at higher frequencies.

At the latter frequencies, the parasitic capacitance discharge losses become excessive. But a modified Class D structure, known as a current-mode Class D (CMCD) PA uses zero voltage switching (ZVS) to minimize discharge losses and can work at higher frequencies. 5-8 Most current-mode Class D PAs have been fabricated with gallium arsenide (GaAs) field-effect transistors (FETs)5, 6 or silicon lateral diffused metal-oxide-semiconductor (LDMO) FETs.

7, 8 The use of these technologies prevents fabrication as a silicon CMOS chip. A two-stage amplifier was designed for high efficiency in a silicon CMOS process. The first, driver stage accepts input current signals and converts them to larger driving signals for the following stage. The second stage is basically a PA. Spiral inductors were used to allow the use of on-chip inductors. For analysis, the amplifier design was simulated using the Cadence Spectre ® CAE program for a CHRT 0.

18- m mixed-signal/RF CMOS process. The simulations revealed that this PA design offers higher efficiency and output power than other CMOS PAs working at the same frequency. 9-13 Figure 1 presents the circuit for this high-efficiency CMOS PA. The driver 🔗 External reference