Frequency counter Counter schematic

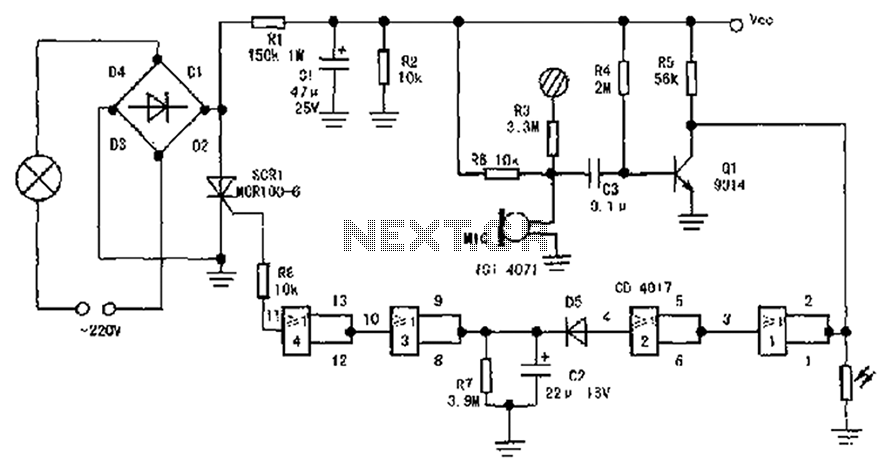

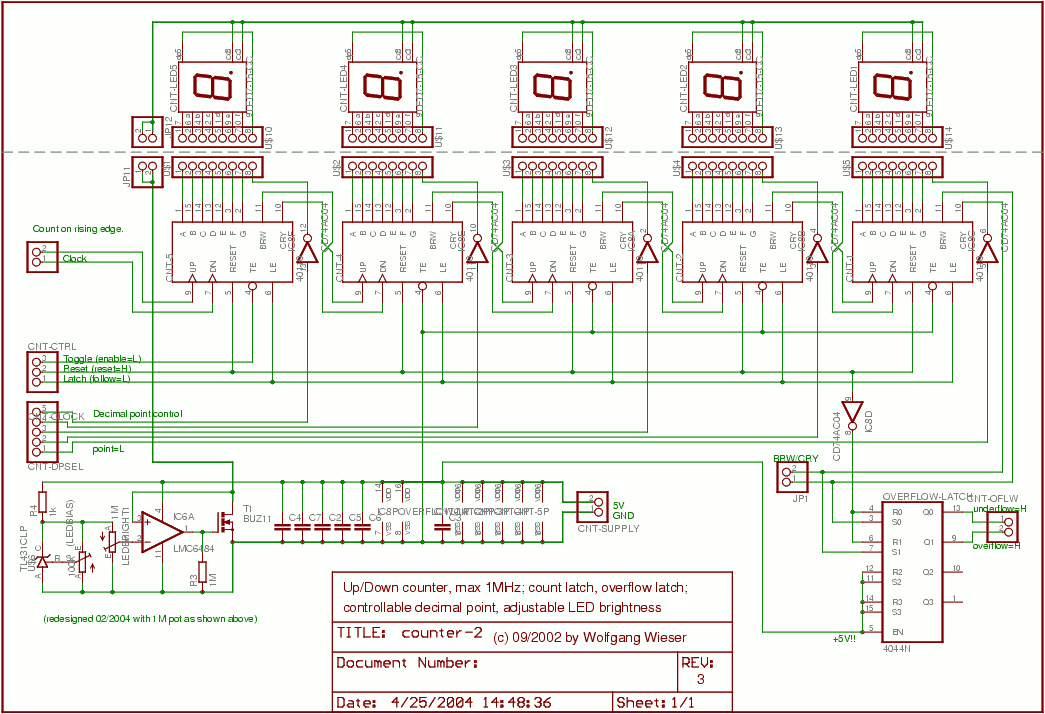

The counter utilizes five cascaded CD40110 chips, which integrate a decade counter, a display latch, and a 7-segment LED driver within a single package. The decimal points are driven by an IC8x. This counter supports both up and down counting, although only up counting is employed in the frequency counter, and it counts on the rising edge of the input signal. An overflow and underflow indicator is provided via a CD4044, which feeds back to the logic board, enabling automatic adjustment of the divider or gate time in the event of an overflow. During normal operations, such as frequency or time measurement, the CD40110 chips count the input signals in the background while still displaying the previous content. Once the measurement is complete, the logic board sends a LOW pulse to the latch input of CNT-CTRL to transfer the counter content into the display latches, allowing it to be shown on the LEDs. Subsequently, a HIGH pulse is sent to the reset line to reset the counter and the overflow indicator. The toggle line is available to enable the up/down clock but is not utilized in the frequency counter. The circuit located at the bottom left is intended to provide a constant voltage sink for the LEDs; however, it does not function as expected and may exhibit fluctuations.

The circuit design employs five CD40110 integrated circuits, which are known for their versatility in digital counting applications. Each CD40110 chip contains a decade counter that can count from 0 to 9 and includes the necessary logic to control the display and manage the counting process. The cascading of these chips allows for the counting of larger numbers, as the output of one chip can serve as the clock input for the next, creating a multi-digit counter system.

The counting mechanism operates on the principle of detecting the rising edge of the input signal, which triggers the counting process. This feature is critical for applications requiring precise timing and frequency measurement. The integration of a display latch allows for the temporary storage of the counted value, enabling the display to show the last counted number until the measurement is completed.

The CD4044 serves an essential role in managing the overflow and underflow conditions of the counting process. By providing feedback to the logic board, it ensures that the counting system can adapt dynamically to changes in input frequency, thus maintaining accuracy in measurements. This adaptability is crucial in applications where input signals may vary significantly.

The logic board's operation is further refined by the use of control pulses. A LOW pulse directed to the CNT-CTRL latch input transfers the current count value to the display, allowing the user to view the result immediately after measurement completion. Following this, a HIGH pulse resets the counter, preparing it for the next counting cycle. The toggle line, while available for enabling up/down counting, remains unused in this specific application, which simplifies the design and focuses on the up counting functionality.

The design also incorporates a voltage sink circuit for the LED displays. This circuit is intended to provide a stable voltage to the LEDs, ensuring consistent brightness and performance. However, the current implementation has been noted to produce undesired fluctuations, indicating that further refinement or redesign may be necessary to achieve the desired stability in LED operation. A more reliable voltage regulation approach would enhance the overall functionality of the display system, ensuring that it meets the performance expectations in various operating conditions.The counter makes use of 5 cascaded CD40110 which combine a decade counter, a display latch and a 7 segment LED driver in a single chip. (The decimal points are driven by IC8x. ) The counter allows up and down counting (although only up counting is used in the frequency counter) and counts on the rising edge.

An over- and underflow indicator is pro vided via CD4044 which is fed back to the logic board to allow automatic adaption of the divider or gate time if the counter has an overflow. In normal (e. g. frequency or time measurement) operation, CD40110 is used to count the input signals "in background" while still displaying the old content.

Then, when the measurement is done, the logic board provides a LOW pulse on the latch input of CNT-CTRL to put the counter content into the display latches and hence display it on the LEDs, then reset the counter (and overflow indicator) using a HIGH pulse to the reset line. The toggle line can be used to enable the up/down clock but is not used in the frequency counter. The circuit on the left bottom is thought to provide a constant voltage sink for the LEDs. Better invent something similar since this circuit does not really work as expected and may tend to swing.

🔗 External reference

The circuit design employs five CD40110 integrated circuits, which are known for their versatility in digital counting applications. Each CD40110 chip contains a decade counter that can count from 0 to 9 and includes the necessary logic to control the display and manage the counting process. The cascading of these chips allows for the counting of larger numbers, as the output of one chip can serve as the clock input for the next, creating a multi-digit counter system.

The counting mechanism operates on the principle of detecting the rising edge of the input signal, which triggers the counting process. This feature is critical for applications requiring precise timing and frequency measurement. The integration of a display latch allows for the temporary storage of the counted value, enabling the display to show the last counted number until the measurement is completed.

The CD4044 serves an essential role in managing the overflow and underflow conditions of the counting process. By providing feedback to the logic board, it ensures that the counting system can adapt dynamically to changes in input frequency, thus maintaining accuracy in measurements. This adaptability is crucial in applications where input signals may vary significantly.

The logic board's operation is further refined by the use of control pulses. A LOW pulse directed to the CNT-CTRL latch input transfers the current count value to the display, allowing the user to view the result immediately after measurement completion. Following this, a HIGH pulse resets the counter, preparing it for the next counting cycle. The toggle line, while available for enabling up/down counting, remains unused in this specific application, which simplifies the design and focuses on the up counting functionality.

The design also incorporates a voltage sink circuit for the LED displays. This circuit is intended to provide a stable voltage to the LEDs, ensuring consistent brightness and performance. However, the current implementation has been noted to produce undesired fluctuations, indicating that further refinement or redesign may be necessary to achieve the desired stability in LED operation. A more reliable voltage regulation approach would enhance the overall functionality of the display system, ensuring that it meets the performance expectations in various operating conditions.The counter makes use of 5 cascaded CD40110 which combine a decade counter, a display latch and a 7 segment LED driver in a single chip. (The decimal points are driven by IC8x. ) The counter allows up and down counting (although only up counting is used in the frequency counter) and counts on the rising edge.

An over- and underflow indicator is pro vided via CD4044 which is fed back to the logic board to allow automatic adaption of the divider or gate time if the counter has an overflow. In normal (e. g. frequency or time measurement) operation, CD40110 is used to count the input signals "in background" while still displaying the old content.

Then, when the measurement is done, the logic board provides a LOW pulse on the latch input of CNT-CTRL to put the counter content into the display latches and hence display it on the LEDs, then reset the counter (and overflow indicator) using a HIGH pulse to the reset line. The toggle line can be used to enable the up/down clock but is not used in the frequency counter. The circuit on the left bottom is thought to provide a constant voltage sink for the LEDs. Better invent something similar since this circuit does not really work as expected and may tend to swing.

🔗 External reference