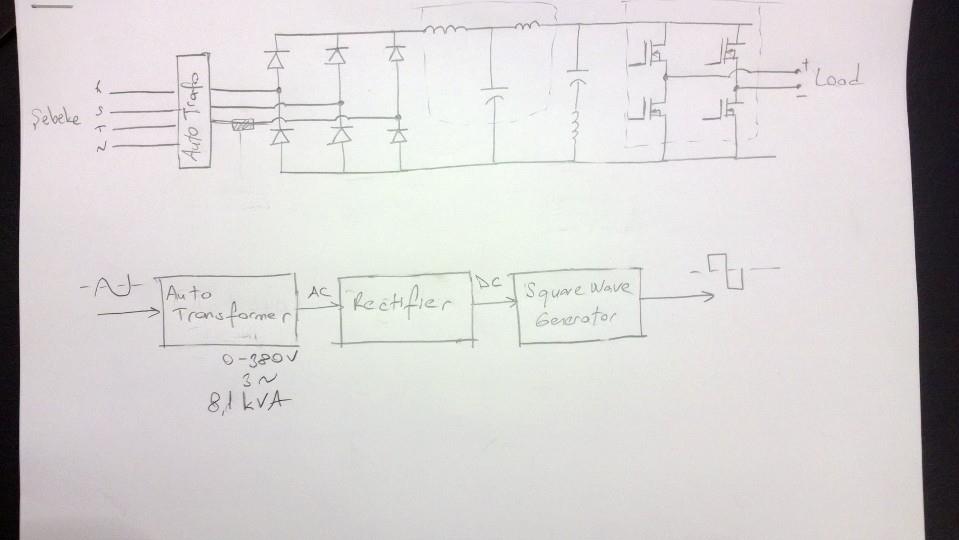

High Power Square Wave Generator (0-500V 25A)

V1 and V2 are set to 5V in the simulation, but they could also be set to 10V to eliminate the need for a second power supply. Alternatively, if logic level FETs can be sourced at that higher voltage, the 10V supply can be reduced to 5V. Assuming the switching frequency is low enough (maximum of 100 Hz), it may be beneficial to use SCRs or similar devices, as they are more suited for this application. These devices are commonly used in inverters to generate stepped square waves that approximate a sine wave. Additionally, a parallel combination of solid-state relays might effectively handle the total current, potentially offering better performance than an H-bridge MOSFET configuration since the relays will be in series with the load and will exhibit minimal voltage drop when activated. When deactivated, the current will be nearly zero. The primary challenge is to generate a 500V DC rail at 25A, which corresponds to a minimum or average power requirement of 6250W, assuming a 50% duty cycle, leading to a total of over 7kW when accounting for losses.

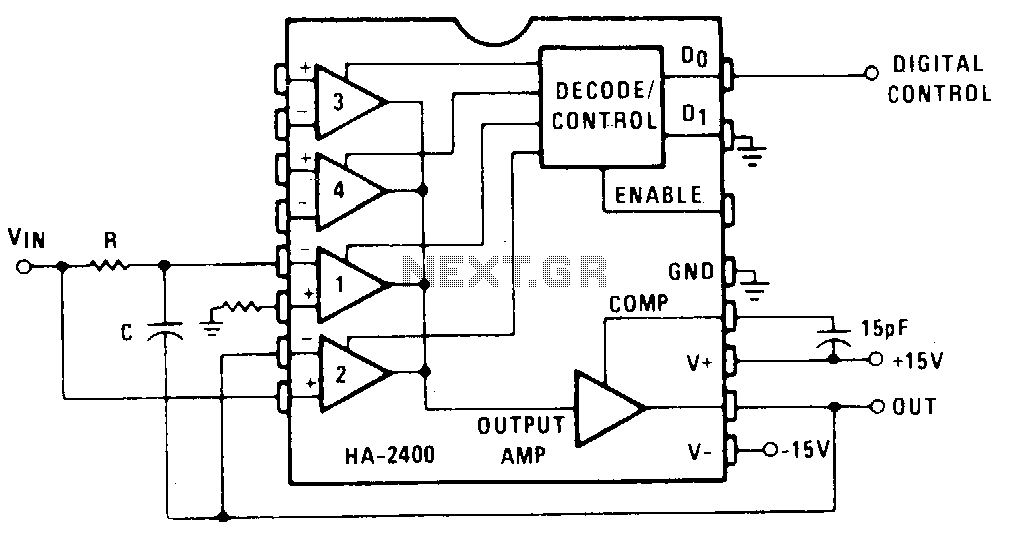

In this circuit design, two voltage sources, V1 and V2, are essential for the operation of the system. The selection of either 5V or 10V for these sources is crucial, as it impacts the overall efficiency and complexity of the circuit. Utilizing a higher voltage may reduce the number of required power supplies, simplifying the design. The use of logic level FETs is recommended if they are available at the required voltage, as they can provide efficient switching capabilities.

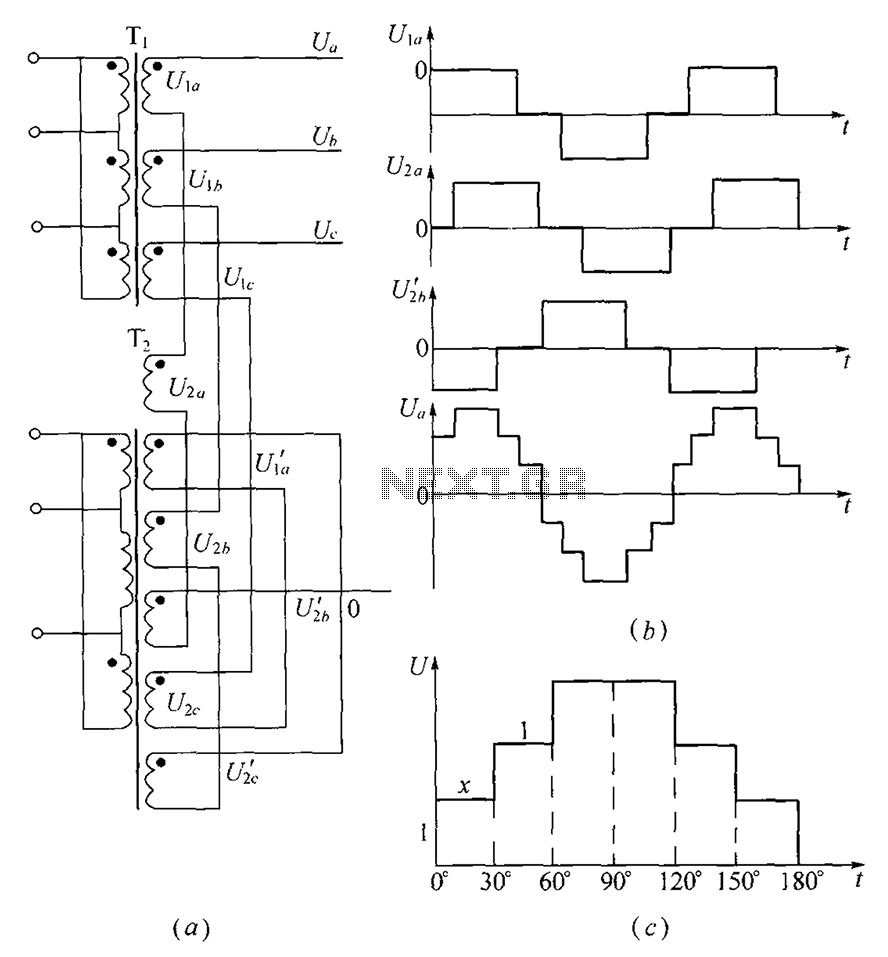

For applications with a low switching frequency (up to 100 Hz), Silicon Controlled Rectifiers (SCRs) or similar devices are advantageous due to their ability to handle high power and provide robust performance in inverter applications. SCRs can effectively generate stepped square waves, which serve to approximate a sine wave output, making them suitable for power applications where waveform quality is less critical.

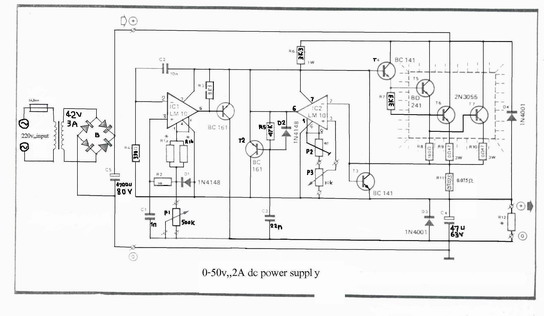

The incorporation of solid-state relays in parallel can enhance the circuit's ability to manage high currents. This configuration is beneficial as it minimizes the voltage drop across the relays when they are in the ON state, ensuring that the load receives the maximum possible voltage. Furthermore, when the relays are OFF, they present a very high impedance, resulting in negligible current flow, which is advantageous for power savings and reducing heat generation.

The most significant challenge in this design is generating a 500V DC rail capable of delivering 25A of current. This requirement translates to a minimum average power output of 6250W. Considering a 50% duty cycle, the effective power requirement may exceed 7kW when factoring in losses within the system. Therefore, careful attention must be given to the design of the power supply and the components used to ensure they can handle the expected load without failure. Proper thermal management and component ratings must be considered to maintain reliability and efficiency in the overall circuit operation.V1 and V2 are set to 5V in the simulation, but could also be 10V to eliminate the need for a second supply ” or, if you can find logic level FETs at that high a voltage, then you can reduce the 10 volt supply to 5 volts. Assuming that the switching frequency is low enough (100 Hz max), why not use SCRs or a similar class of devices I believe these would be better

suited to this kind of work (they are used in inverters to generate stepped square waves to approximate a sine wave). Also perhaps a paralleled combination of solid-state relays might be able to handle the total current this will probably be better than the H-bridge MOSFET scheme since the relays will appear in series with the load and won`t have much drop across them when ON.

When OFF, the current will be almost nil. The main problem is to first generate the 500V DC rail at 25A that represents minimum or average power requirement of 6250W assuming 50% duty cycle almost 7kW+ when we consider losses. 🔗 External reference

In this circuit design, two voltage sources, V1 and V2, are essential for the operation of the system. The selection of either 5V or 10V for these sources is crucial, as it impacts the overall efficiency and complexity of the circuit. Utilizing a higher voltage may reduce the number of required power supplies, simplifying the design. The use of logic level FETs is recommended if they are available at the required voltage, as they can provide efficient switching capabilities.

For applications with a low switching frequency (up to 100 Hz), Silicon Controlled Rectifiers (SCRs) or similar devices are advantageous due to their ability to handle high power and provide robust performance in inverter applications. SCRs can effectively generate stepped square waves, which serve to approximate a sine wave output, making them suitable for power applications where waveform quality is less critical.

The incorporation of solid-state relays in parallel can enhance the circuit's ability to manage high currents. This configuration is beneficial as it minimizes the voltage drop across the relays when they are in the ON state, ensuring that the load receives the maximum possible voltage. Furthermore, when the relays are OFF, they present a very high impedance, resulting in negligible current flow, which is advantageous for power savings and reducing heat generation.

The most significant challenge in this design is generating a 500V DC rail capable of delivering 25A of current. This requirement translates to a minimum average power output of 6250W. Considering a 50% duty cycle, the effective power requirement may exceed 7kW when factoring in losses within the system. Therefore, careful attention must be given to the design of the power supply and the components used to ensure they can handle the expected load without failure. Proper thermal management and component ratings must be considered to maintain reliability and efficiency in the overall circuit operation.V1 and V2 are set to 5V in the simulation, but could also be 10V to eliminate the need for a second supply ” or, if you can find logic level FETs at that high a voltage, then you can reduce the 10 volt supply to 5 volts. Assuming that the switching frequency is low enough (100 Hz max), why not use SCRs or a similar class of devices I believe these would be better

suited to this kind of work (they are used in inverters to generate stepped square waves to approximate a sine wave). Also perhaps a paralleled combination of solid-state relays might be able to handle the total current this will probably be better than the H-bridge MOSFET scheme since the relays will appear in series with the load and won`t have much drop across them when ON.

When OFF, the current will be almost nil. The main problem is to first generate the 500V DC rail at 25A that represents minimum or average power requirement of 6250W assuming 50% duty cycle almost 7kW+ when we consider losses. 🔗 External reference