High speed paper tape reader

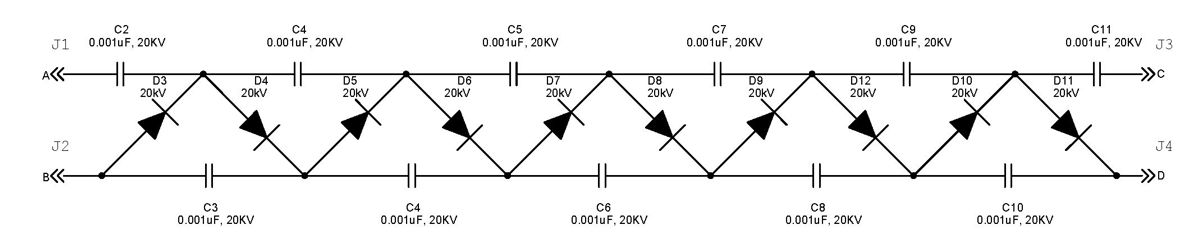

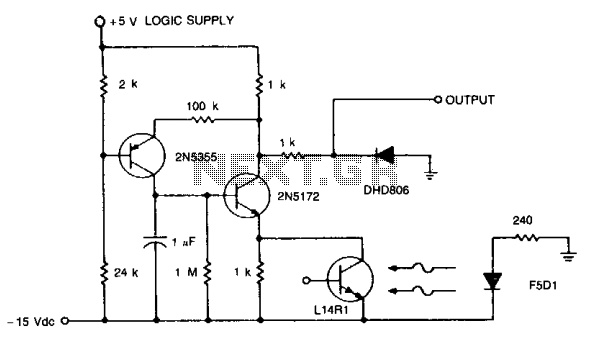

When interfacing computer peripheral equipment, it is advantageous to utilize logic signal levels. This circuit operates with a nominal output of 4 V, which drops to -0.6 V upon illumination, meeting the specifications for a high-speed optical reader system for paper tape. The circuit can function at speeds of up to 1000 bits per second and is designed to operate with tape translucency that allows 50% of the incident light to reach the sensor. It provides a fixed threshold signal to the logic circuit while maintaining low costs. Several techniques are employed in the design. The speed of the photodarlington is enhanced through cascode constant voltage biasing.

The output threshold and tape translucency requirements are met by monitoring the output voltage and enabling operation at 2000 bits per second under ambient light levels equivalent to signal levels.

The described circuit is structured to facilitate the reliable interfacing of peripheral devices through the use of logic signal levels, which are essential for digital communication. The nominal output voltage of 4 V signifies a logic high state, while the drop to -0.6 V indicates a logic low state when the optical sensor is illuminated by the tape. This behavior is crucial for accurately reading data from high-speed paper tape optical readers.

Operating at speeds up to 1000 bits per second allows for efficient data transmission, while the capability to handle tape translucency that transmits 50% of incident light ensures versatility in various lighting conditions. The design emphasizes cost-effectiveness without compromising performance, making it suitable for applications where budget constraints are a consideration.

The implementation of cascode constant voltage biasing serves to enhance the response time of the photodarlington transistor, thereby improving the overall speed and efficiency of the optical reading process. This configuration minimizes the effects of voltage variations and optimizes the sensor's performance, ensuring that it reliably detects the light signals corresponding to the data encoded on the tape.

Moreover, the ability to operate at 2000 bits per second under ambient light levels comparable to signal levels indicates that the circuit is robust against noise and fluctuations in the environment. By continuously monitoring the output voltage, the circuit can dynamically adjust to maintain the required threshold for accurate data interpretation. This adaptability is particularly beneficial in real-world applications where lighting conditions may vary significantly.

In summary, this circuit design not only meets the fundamental requirements for interfacing with computer peripherals but also incorporates advanced techniques to enhance performance, making it a reliable solution for high-speed optical reading applications.When computer peripheral equipment is interfaced, it is convenient to work with logic signal levels. With a nominal 4 V at the output dropping to - 0.6 V on illumination, this circuit reflects the requirements of a high-speed, paper tape optical reader system. The circuit operates at rates of up to 1000 bits per second. It will also operate at tape translucency such that 50% of the incident light is transmitted to the sensor, and provide a fixed threshold signal to the logic circuit, all at low cost.

Several circuit tricks are required. Photodarlington speed is enhanced by cascode constant voltage biasing. The output threshold and tape translucency requirements are provided for by sensing the output voltage and operating to 2000 bits per second at ambient light levels equal to signal levels.

The output threshold and tape translucency requirements are met by monitoring the output voltage and enabling operation at 2000 bits per second under ambient light levels equivalent to signal levels.

The described circuit is structured to facilitate the reliable interfacing of peripheral devices through the use of logic signal levels, which are essential for digital communication. The nominal output voltage of 4 V signifies a logic high state, while the drop to -0.6 V indicates a logic low state when the optical sensor is illuminated by the tape. This behavior is crucial for accurately reading data from high-speed paper tape optical readers.

Operating at speeds up to 1000 bits per second allows for efficient data transmission, while the capability to handle tape translucency that transmits 50% of incident light ensures versatility in various lighting conditions. The design emphasizes cost-effectiveness without compromising performance, making it suitable for applications where budget constraints are a consideration.

The implementation of cascode constant voltage biasing serves to enhance the response time of the photodarlington transistor, thereby improving the overall speed and efficiency of the optical reading process. This configuration minimizes the effects of voltage variations and optimizes the sensor's performance, ensuring that it reliably detects the light signals corresponding to the data encoded on the tape.

Moreover, the ability to operate at 2000 bits per second under ambient light levels comparable to signal levels indicates that the circuit is robust against noise and fluctuations in the environment. By continuously monitoring the output voltage, the circuit can dynamically adjust to maintain the required threshold for accurate data interpretation. This adaptability is particularly beneficial in real-world applications where lighting conditions may vary significantly.

In summary, this circuit design not only meets the fundamental requirements for interfacing with computer peripherals but also incorporates advanced techniques to enhance performance, making it a reliable solution for high-speed optical reading applications.When computer peripheral equipment is interfaced, it is convenient to work with logic signal levels. With a nominal 4 V at the output dropping to - 0.6 V on illumination, this circuit reflects the requirements of a high-speed, paper tape optical reader system. The circuit operates at rates of up to 1000 bits per second. It will also operate at tape translucency such that 50% of the incident light is transmitted to the sensor, and provide a fixed threshold signal to the logic circuit, all at low cost.

Several circuit tricks are required. Photodarlington speed is enhanced by cascode constant voltage biasing. The output threshold and tape translucency requirements are provided for by sensing the output voltage and operating to 2000 bits per second at ambient light levels equal to signal levels.