Improved non-inverting integrator

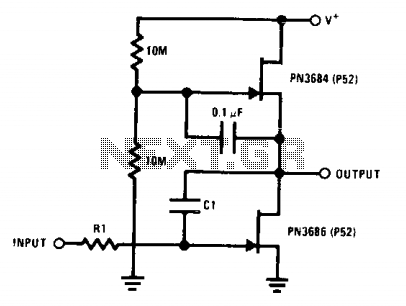

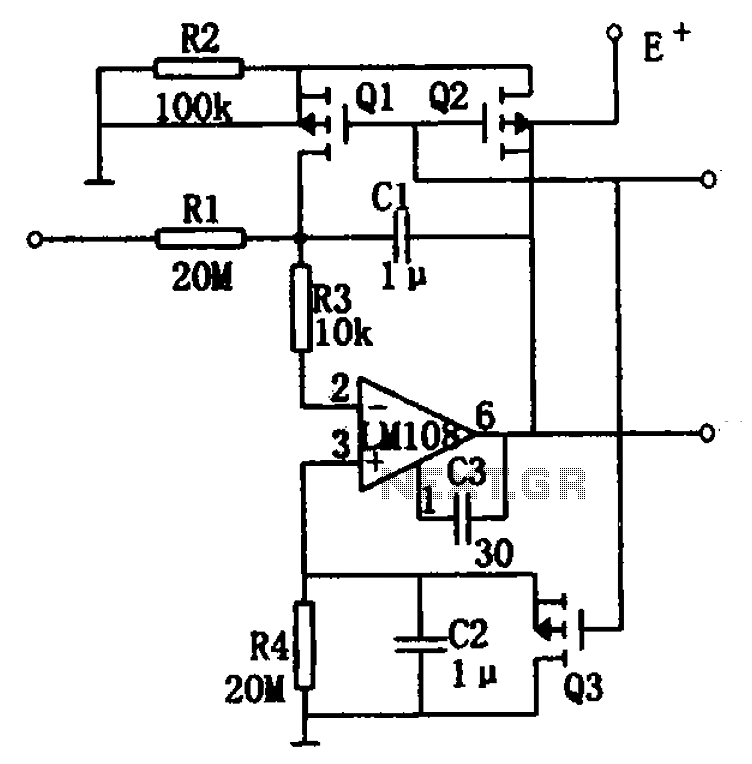

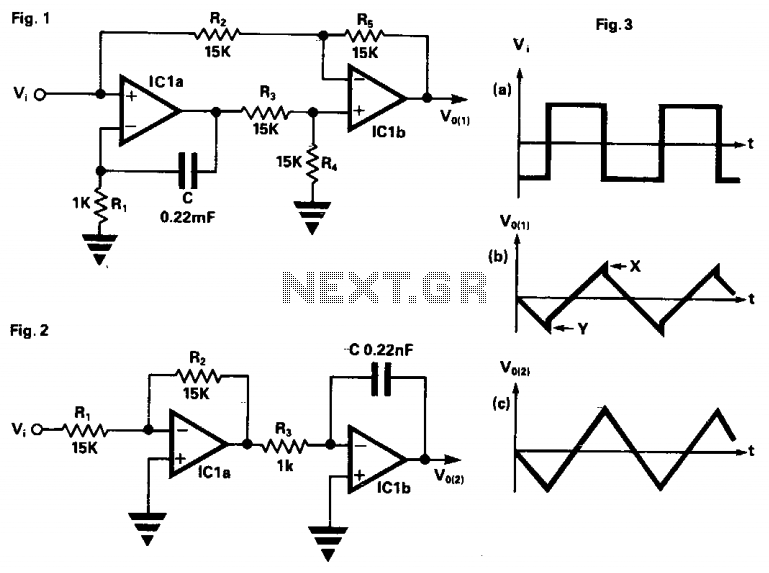

In the circuit depicted in Figure 1, ICla generates the integral term required for operation, but it also inadvertently produces an unnecessary proportional term. This proportional term is countered by IClb, resulting in a pure integral output. If the ratio R2/R5 does not precisely match the ratio of R3/R4, the subtraction will be incomplete, allowing a small amount of the proportional term to appear at the output. This effect is illustrated in Figure 3a, where small steps in the output waveform can be observed at points X and Y when a square wave input is applied. This issue can be entirely mitigated by employing the simplified circuit shown in Figure 2, where the signal is first inverted by ICla and then directed to a standard inverting integrator IClb.

The modified circuit configuration presents a non-inverting integrator that eliminates the generation of the unwanted proportional term altogether, thereby negating the need for subtraction. In this design, ICla acts as a pre-inverter, processing the input signal before it reaches IClb. This pre-inversion ensures that the integrator operates solely on the integral component of the input signal, thereby enhancing the accuracy and performance of the circuit.

The implementation of this design not only simplifies the overall circuit but also improves the reliability of the output waveform. By removing the proportional term from the equation, the integrator can maintain a consistent response to varying input signals without introducing distortion or unwanted artifacts. The resulting output is a clean, smooth waveform that accurately reflects the integral of the input signal, making this configuration particularly advantageous in applications where precision is critical.

In summary, the transition from a standard integrator configuration to a non-inverting integrator through the use of ICla and IClb demonstrates a significant improvement in performance by addressing the issues associated with unwanted proportional terms. This refined approach highlights the importance of circuit design optimization in achieving high-fidelity electronic signal processing.In the circuit in Fig. 1, ICla produces the integral term required but also has the side effect of producing a proportional term not required, so this term is subtracted by IClb leaving a pure integral. If the ratio R2/R5 does not exactly match the ratio of R3/R4, the subtraction will not be complete and a small amount of the proportional term will reach the output.

The result of this with a square wave input is shown in Fig. 3a as small steps in the output waveform at points X and Y. This effect can be completely removed by using the simplified circuit shown in Fig. 2. Here the signal is pre-inverted by ICla, then fed to a standard inverting integrator IClb. The result is a non-inverting integrator with the advantage that the unwanted proportional term is never produced, so it does not need to be subtracted. 🔗 External reference

The modified circuit configuration presents a non-inverting integrator that eliminates the generation of the unwanted proportional term altogether, thereby negating the need for subtraction. In this design, ICla acts as a pre-inverter, processing the input signal before it reaches IClb. This pre-inversion ensures that the integrator operates solely on the integral component of the input signal, thereby enhancing the accuracy and performance of the circuit.

The implementation of this design not only simplifies the overall circuit but also improves the reliability of the output waveform. By removing the proportional term from the equation, the integrator can maintain a consistent response to varying input signals without introducing distortion or unwanted artifacts. The resulting output is a clean, smooth waveform that accurately reflects the integral of the input signal, making this configuration particularly advantageous in applications where precision is critical.

In summary, the transition from a standard integrator configuration to a non-inverting integrator through the use of ICla and IClb demonstrates a significant improvement in performance by addressing the issues associated with unwanted proportional terms. This refined approach highlights the importance of circuit design optimization in achieving high-fidelity electronic signal processing.In the circuit in Fig. 1, ICla produces the integral term required but also has the side effect of producing a proportional term not required, so this term is subtracted by IClb leaving a pure integral. If the ratio R2/R5 does not exactly match the ratio of R3/R4, the subtraction will not be complete and a small amount of the proportional term will reach the output.

The result of this with a square wave input is shown in Fig. 3a as small steps in the output waveform at points X and Y. This effect can be completely removed by using the simplified circuit shown in Fig. 2. Here the signal is pre-inverted by ICla, then fed to a standard inverting integrator IClb. The result is a non-inverting integrator with the advantage that the unwanted proportional term is never produced, so it does not need to be subtracted. 🔗 External reference

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713