P8 CPU Documentatio Hardware

The datapath consists of registers, an ALU, and an internal system bus. Registers are fast memory locations internal to the CPU, distinct from main system memory, and serve as temporary storage during calculations. The ALU is a combinational logic device that executes arithmetic and logical operations on data. The internal bus facilitates data exchange between the ALU and registers. The control section interprets each instruction to be executed and asserts the datapath's control signals in the correct sequence to implement the instruction. After executing an instruction, it moves on to the next one. Various requirements and constraints were imposed on the hardware, some of which were contradictory, leading to compromises favoring reduced cost and/or construction time. It must meet specifications outlined in Section 2.5 and implement the complete instruction set described in Section 3.7 without compromise. The programmer's model defines the architecture of a computer, serving as a high-level "machine" visible to the programmer but independent of the actual hardware. It encompasses the functional behavior of the computer as perceived by the programmer, including the number and sizes of registers, types of instructions, addressing modes, and available memory. The P8 CPU architecture includes three 8-bit registers and one 1-bit condition register. It features an accumulator-based design where the accumulator (A register) serves as an operand for most ALU operations, with all ALU results stored in the A register, overwriting previous contents. The R register is used to store general data or a second operand and holds the memory address of operands for indirect addressing instructions. The instruction pointer, being an 8-bit register, allows addressing of only 256 bytes of memory, with an equal number of available I/O ports that do not share memory space. The Z register, a 1-bit register, holds the result of the last comparison operation, indicating a "1" for zero results and "0" otherwise. An 8-bit ALU is required to implement arithmetic and logical instructions, necessitating two 4-bit ALUs (the 74181). This ALU generates condition bits for carry, half-carry, A=B (or zero), A>B, and A<B, although only the zero condition bit is implemented in the P8 CPU to demonstrate conditional branching. The "A=B" output is open collector and must be connected to an external resistor, going high when the A and B inputs are equal during a P8 compare instruction. The "CN+4" output of the least significant 4-bit ALU connects to the "CN" input of the most significant 4-bit ALU, forming an 8-bit ALU and allowing a carry between bit 3 (MSB of the first ALU) and bit 4 (LSB of the second ALU) for accurate 8-bit results. The "CN" of the least significant ALU must be low for subtraction and high for other operations. This input, along with select and mode inputs, is controlled by the CPU's control logic, which configures all inputs for the desired ALU operation. The control logic receives inputs from the instruction register (IR) and the ALU (via Z) and generates all necessary control signals for the proper operation of the datapath.

The P8 CPU's architecture is designed to optimize the interaction between its components, ensuring efficient processing of instructions. The registers play a crucial role in high-speed data handling, allowing for quick access and modification during computation. The ALU's design, utilizing two 4-bit units, enables the execution of a comprehensive range of arithmetic and logical operations, essential for the CPU's functionality. The careful arrangement of control signals ensures that the ALU operates correctly, responding to the current instruction's demands while maintaining synchronization with the internal bus and registers.

The conditional logic implemented through the Z register facilitates basic decision-making processes within the CPU, allowing it to branch based on the results of operations. This capability is fundamental for executing more complex algorithms and control structures within programs. The architecture's limitation of 256 bytes of addressable memory and 256 I/O ports reflects a design choice that balances complexity and cost, making the P8 CPU suitable for specific applications while highlighting the trade-offs inherent in hardware design.

Overall, the P8 CPU's architecture exemplifies a well-structured approach to CPU design, focusing on efficient data handling, robust operational capabilities, and a clear separation of functional components, all of which contribute to its effectiveness in executing a defined instruction set.The datapath contains registers, an ALU, and an internal system bus. Registers are very fast memory locations that are internal to the CPU and separate from the main system memory. They can be used as "scratch pads" during calculations. The ALU is a combinational logic device that performs arithmetic and logical operations on data. The internal bus p ermits data exchange between the ALU and registers. The control section interprets each instruction to be executed and asserts the datapath`s control signals in the proper sequence to implement the instruction. After executing an instruction, it proceeds to the next instruction. The following requirements and constraints were placed upon the hardware. In some cases they were contradictory, and a compromise was reached that favored reduced cost and/or construction time.

1. It must, of course, meet the specifications outlined in Section 2. 5 and implement the complete instruction set described in Section 3. 7. No compromise on this point is permissible. The programmer`s model defines the architecture of a computer. t is a high-level "machine" that is visible to the programmer, but independent of the actual physical hardware. It deals with the functional behavior of the computer as seen by the programmer. It includes the number and sizes of registers, types of instructions, addressing modes, and available memory.

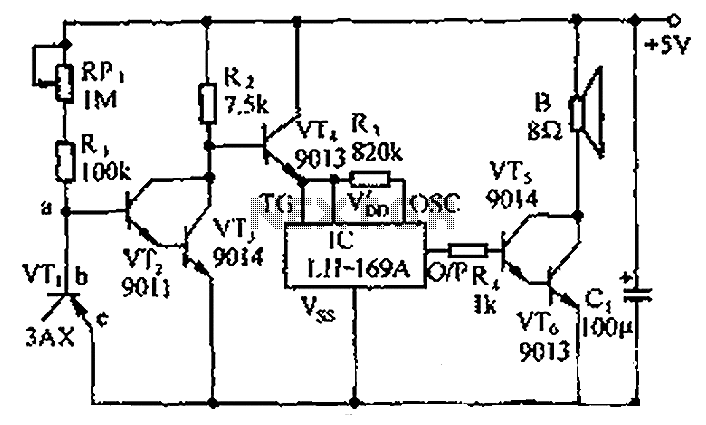

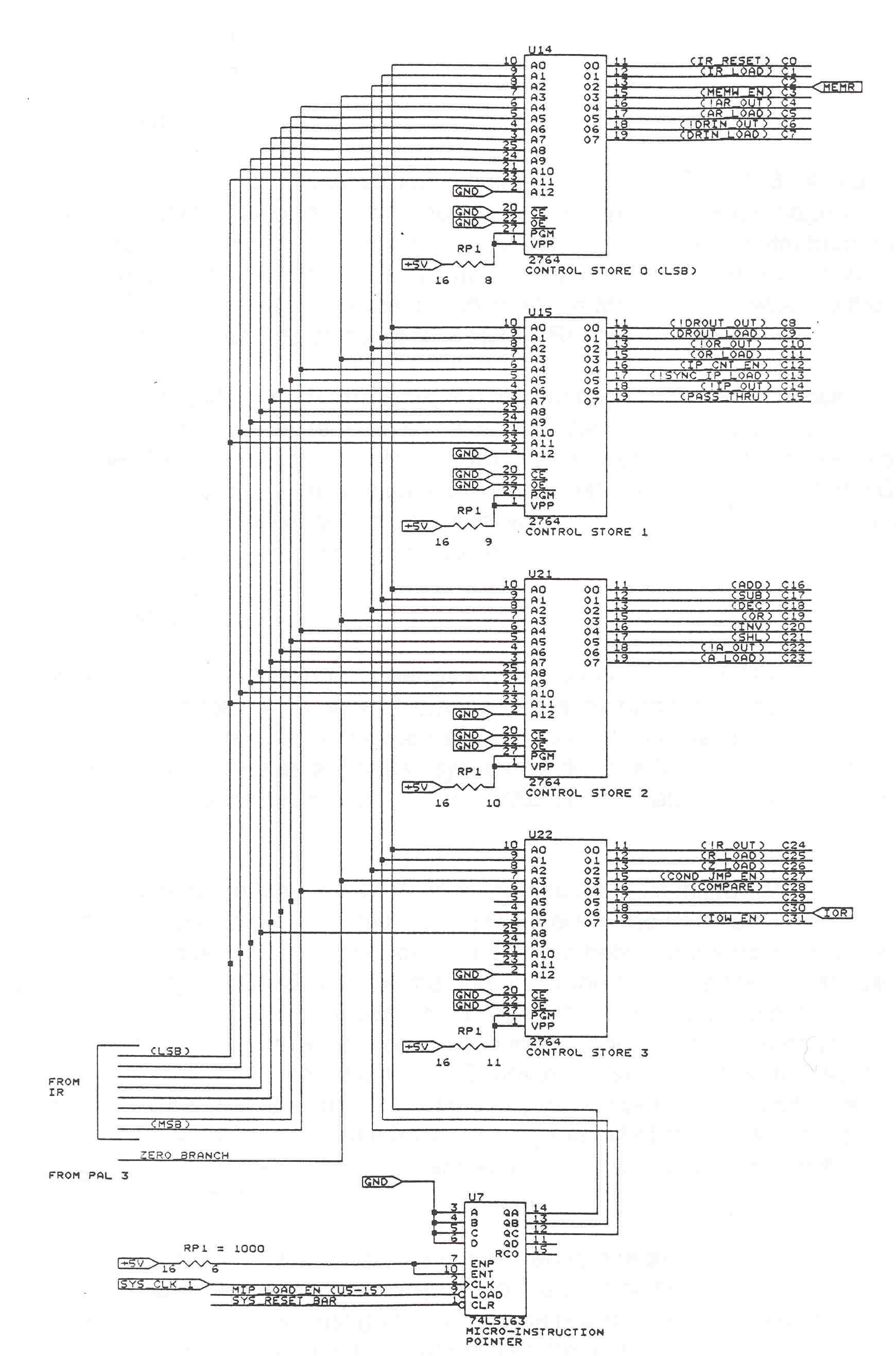

See Section 3 for more information on many of the architectural features of the P8 CPU. The P8 CPU consists of three 8-bit registers and one 1-bit condition register. See Figure 4. 1. It is an accumulator-based design. This means that the number in the accumulator (A register) is an operand for most ALU operations. Additionally, all ALU results are placed in the A register, and overwrite its previous contents. It is also used for reading input ports and writing output ports. The R register may be used to store general data or a second operand. It also contains the memory address of operands for instructions using indirect addressing. Because the instruction pointer is an 8-bit register, only 256 bytes of memory may be addressed. Similarly, there are 256 available I/O ports, which do not share the memory space. The Z register is a 1-bit register that stores the results of the last compare operation. If the result was zero, the Z register contains a "1", otherwise it is "0". One 8-bit ALU is needed to implement the arithmetic and logical instructions. Actually, the decision of which ALU instructions to include in the instruction set was dictated by the only TTL ALU available - the 74181. Because this is a 4-bit ALU, two of them are required. See Figure 4. 4. This ALU can generate condition bits for carry, half-carry, A=B (or zero), A>B, and A

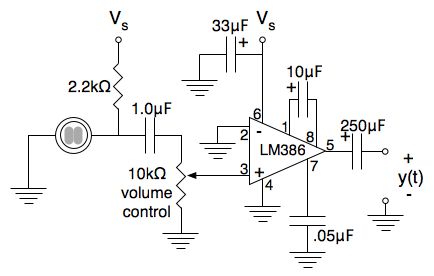

) The "CN+4" output of the least significant 4-bit ALU must be connected to the "CN" input of the most significant 4-bit ALU to create an 8-bit ALU. This connection allows a carry between bit 3 (MSB of first ALU) and bit 4 (LSB of second ALU) and generates the correct 8-bit result during an ALU operation.

"CN" of the least significant ALU must be low for a subtract operation and high for all others. This input, as well as the select and mode inputs, are asserted by the control logic of the CPU. The control logic properly configures all inputs for the desired ALU operation. The control logic accepts inputs from IR and the ALU (through Z) and generates as output all the control signals necessary for the correct operation of the datapath. There are two approaches that can b 🔗 External reference

The P8 CPU's architecture is designed to optimize the interaction between its components, ensuring efficient processing of instructions. The registers play a crucial role in high-speed data handling, allowing for quick access and modification during computation. The ALU's design, utilizing two 4-bit units, enables the execution of a comprehensive range of arithmetic and logical operations, essential for the CPU's functionality. The careful arrangement of control signals ensures that the ALU operates correctly, responding to the current instruction's demands while maintaining synchronization with the internal bus and registers.

The conditional logic implemented through the Z register facilitates basic decision-making processes within the CPU, allowing it to branch based on the results of operations. This capability is fundamental for executing more complex algorithms and control structures within programs. The architecture's limitation of 256 bytes of addressable memory and 256 I/O ports reflects a design choice that balances complexity and cost, making the P8 CPU suitable for specific applications while highlighting the trade-offs inherent in hardware design.

Overall, the P8 CPU's architecture exemplifies a well-structured approach to CPU design, focusing on efficient data handling, robust operational capabilities, and a clear separation of functional components, all of which contribute to its effectiveness in executing a defined instruction set.The datapath contains registers, an ALU, and an internal system bus. Registers are very fast memory locations that are internal to the CPU and separate from the main system memory. They can be used as "scratch pads" during calculations. The ALU is a combinational logic device that performs arithmetic and logical operations on data. The internal bus p ermits data exchange between the ALU and registers. The control section interprets each instruction to be executed and asserts the datapath`s control signals in the proper sequence to implement the instruction. After executing an instruction, it proceeds to the next instruction. The following requirements and constraints were placed upon the hardware. In some cases they were contradictory, and a compromise was reached that favored reduced cost and/or construction time.

1. It must, of course, meet the specifications outlined in Section 2. 5 and implement the complete instruction set described in Section 3. 7. No compromise on this point is permissible. The programmer`s model defines the architecture of a computer. t is a high-level "machine" that is visible to the programmer, but independent of the actual physical hardware. It deals with the functional behavior of the computer as seen by the programmer. It includes the number and sizes of registers, types of instructions, addressing modes, and available memory.

See Section 3 for more information on many of the architectural features of the P8 CPU. The P8 CPU consists of three 8-bit registers and one 1-bit condition register. See Figure 4. 1. It is an accumulator-based design. This means that the number in the accumulator (A register) is an operand for most ALU operations. Additionally, all ALU results are placed in the A register, and overwrite its previous contents. It is also used for reading input ports and writing output ports. The R register may be used to store general data or a second operand. It also contains the memory address of operands for instructions using indirect addressing. Because the instruction pointer is an 8-bit register, only 256 bytes of memory may be addressed. Similarly, there are 256 available I/O ports, which do not share the memory space. The Z register is a 1-bit register that stores the results of the last compare operation. If the result was zero, the Z register contains a "1", otherwise it is "0". One 8-bit ALU is needed to implement the arithmetic and logical instructions. Actually, the decision of which ALU instructions to include in the instruction set was dictated by the only TTL ALU available - the 74181. Because this is a 4-bit ALU, two of them are required. See Figure 4. 4. This ALU can generate condition bits for carry, half-carry, A=B (or zero), A>B, and A

) The "CN+4" output of the least significant 4-bit ALU must be connected to the "CN" input of the most significant 4-bit ALU to create an 8-bit ALU. This connection allows a carry between bit 3 (MSB of first ALU) and bit 4 (LSB of second ALU) and generates the correct 8-bit result during an ALU operation.

"CN" of the least significant ALU must be low for a subtract operation and high for all others. This input, as well as the select and mode inputs, are asserted by the control logic of the CPU. The control logic properly configures all inputs for the desired ALU operation. The control logic accepts inputs from IR and the ALU (through Z) and generates as output all the control signals necessary for the correct operation of the datapath. There are two approaches that can b 🔗 External reference