random number generator game

This electronic game simulates a one-arm bandit game, appealing to electronics hobbyists. When toggle switch S1 is in the 'run' position, all segments of the 7-segment displays (DIS1 through DIS3) illuminate. Upon switching S1 from 'run' to 'stop', the displayed digits continue to advance, resulting in a final display that is unpredictable. Consequently, the final numbers shown in DIS1 through DIS3 are random. The speed at which the numbers in the 7-segment displays change upon flipping S1 from 'run' to 'stop' gradually decays before stabilizing at a random number. To play, participants aim to achieve three identical numbers across the displays. Scoring is as follows: 1 point for a final display of '000', 2 points for '111', 3 points for '222', and up to 10 points for '999'. Players should strive for the maximum possible score within a set number of attempts (e.g., 20 to 25). In addition to its entertainment value, this circuit can function as a random number generator for various applications. The decay time with the specified component values is approximately 15 seconds before the display halts at a final random number. The circuit consists of a clock oscillator based on an NE555 timer IC (IC4), a three-stage clock pulse counter using three CD4033 ICs (IC1 to IC3), and three 7-segment LED displays (DIS1 to DIS3). In the clock oscillator circuit, the NE555 timer IC4 operates as a free-running astable multivibrator, with an additional capacitor C1 connected between pin 7 of IC4 and the junction of resistors R22 and R24. When S1 is in the 'run' position, both terminals of capacitor C1 are shorted by the switch, allowing timer IC4 to function as a free-running astable multivibrator, with an operating frequency around 35 kHz, determined by the timing components. When S1 is flipped to the 'stop' position, capacitor C1 is included in the discharge path of pin 7 of IC4 and the junction of resistors R22 and R24. Simultaneously, capacitor C4 is connected in parallel with timing capacitor C3, altering the operating frequency of the astable from approximately 35 kHz to around 65 Hz. Consequently, capacitor C1 begins to charge, connected in the discharge path of the timing capacitors C3 and C4. The clock frequency of IC4 gradually decreases, and after 15 seconds, when capacitor C1 is adequately charged, the oscillating frequency diminishes until it stops. Thus, pin 3 of IC4 transitions to a low state. The second part of the circuit features three cascaded ICs, IC1 through IC3 (CD4033 decade upcounter and 7-segment decoder). Together with the three 7-segment displays (DIS1 to DIS3), these form a 3-digit clock counter. The clock counting speed is dependent on the clock pulse frequency of IC4, connected to the clock input pin 1 of IC1, while the chip enable pins 2 of IC1 to IC3 are held low. This configuration allows all clock counter ICs to advance by 1 for each positive clock transition. The reset pin 15 of all counter ICs is kept low through resistor R25, thus the reset feature is not utilized in this circuit. Due to persistence of vision, the 0-9 counting in DIS1 to DIS3 is indistinguishable at high clock frequencies, causing all 7-segment displays to appear as digit 8, while the red LED1 remains continuously lit, indicating the clock counter is operational. When the toggle switch S1 is moved from 'run' to 'stop', the counting speed of individual digits decreases immediately as the clock frequency changes to approximately 65 Hz. The counting speeds become 65 Hz for DIS3, 6.5 Hz for DIS2, and 0.6 Hz for DIS1. This gradual decay in counting speed continues until the counter halts, at which point LED1 ceases blinking, and the final random numbers are displayed in DIS1, DIS2, and DIS3.This electronic game is simulation of one-arm bandit game. Electronics hobbyists will find it very interesting. When toggle switch S1 is in run` position, all segments of 7-segment displays (DIS1 through DIS3) will light up. On turning toggle switch S1 from run` to stop` position, displayed digits will continue advancing and the final display is u

npredictable. Thus the final number displayed in DIS1 through DIS3 is of random nature. The speed with which the number in 7-segment display keeps changing on flipping switch S1 from run` to stop` condition slowly decays before stopping with a random number display. To play this game, one has to obtain three identical numbers in displays DIS1 through DIS3. The contestant would score 1 (one) point if he manages to get a final display of 000`, 2 points for getting 111` display, 3 points for 222`, and so on ”up to ten points for 999`.

He should try to score maximum possible points in fixed numbers of attempts (say, 20 to 25 attempts). Apart from using this circuit as a game for entertainment, one can use it as random number generator for any other application as well.

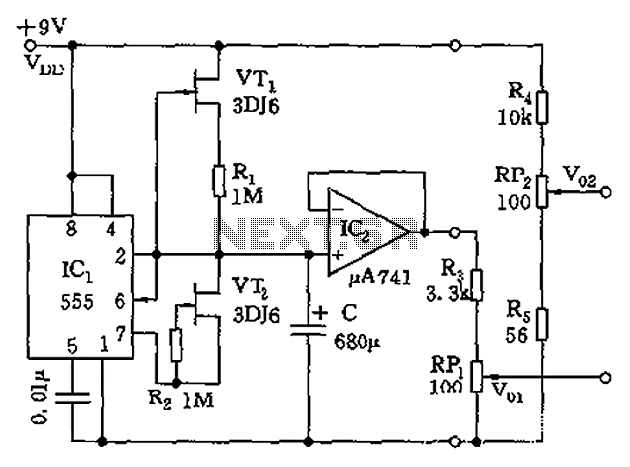

The decay time with the given component values is around 15 seconds before the display could stop at a final random number. The circuit comprises clock oscillator built around NE555 timer IC4, three-stage clock pulse counter built using three CD4033 ICs (IC1 to IC3), and three 7-segment LED displays (DIS1 to DIS3).

In clock oscillator circuit, NE555 timer IC4 is used in a similar way as a free-running astable multivibrator, the only difference being the additional capacitor C1 introduced between pin No. 7 of IC4 and junction of resistors R22 and R24. When toggle switch S1 is in run` position, both terminals of capacitor C1 are shorted by switch S1 and timer IC4 works as a free-running astable multivibrator.

The operating frequency is in the vicinity of 35 kHz, determined by the value of timing components. When toggle switch S1 is flipped from run` to stop` position, capacitor C1 is introduced in the discharge path of pin No. 7 of IC4 and junction of resistors R22 and R24. At the same time, capacitor C4 comes in parallel with timing capacitor C3 to change the operating frequency of the astable from around 35 kHz to around 65 Hz.

Now capacitor C1 slowly starts charging as it is connected in the discharge path of the timing capacitors C3 and C4. The clock frequency of IC4 gradually reduces and after 15 seconds, when capacitor C1 is sufficiently charged, the oscillating frequency gradually drops and finally it stops oscillating.

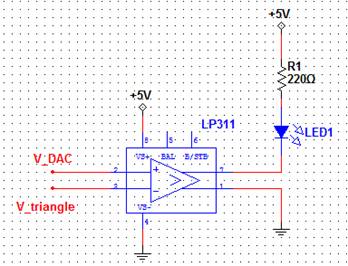

Thus, pin 3 of IC4 becomes low. Second part of the circuit comprises three cascaded ICs, IC1 through IC3 (CD4033 decade upcounter cum 7-segment decoder). In conjunction with three 7-segment displays (DIS1 to DIS3), these form a 3-digit clock counter. The clock counting speed is dependant upon the clock pulse frequency of IC4. It is connected to clock input pin 1 of IC1 while chip enable pin 2 of IC1 to IC3 are held low. Thus all clock counter ICs advance by 1 for every positive clock transition. Reset pin 15 of all counter ICs is held low through resistor R25. Thus reset facility is not used in this circuit. Due to persistence of vision, one can not distinguish 0-9 counting in DIS1 to DIS3 when the clock frequency is high.

All 7-segment displays appear to show digit 8, while the red LED1 remains lit continuously, indicating clock counter is in running condition. On sliding toggle switch S1 from run` to stop` position, the counting speed of individual digits falls immediately due to the clock frequency changing to around 65 Hz.

Now, the counting speed will be 65 Hz for DIS3, 6. 5 Hz for DIS2, and 0. 6 Hz for DIS1. This speed of individual digit counting slowly decays, until the counter stops and LED1 stops blinking, and the final count (random numbers) are displayed in DIS1, DIS2, and DIS3. 🔗 External reference

npredictable. Thus the final number displayed in DIS1 through DIS3 is of random nature. The speed with which the number in 7-segment display keeps changing on flipping switch S1 from run` to stop` condition slowly decays before stopping with a random number display. To play this game, one has to obtain three identical numbers in displays DIS1 through DIS3. The contestant would score 1 (one) point if he manages to get a final display of 000`, 2 points for getting 111` display, 3 points for 222`, and so on ”up to ten points for 999`.

He should try to score maximum possible points in fixed numbers of attempts (say, 20 to 25 attempts). Apart from using this circuit as a game for entertainment, one can use it as random number generator for any other application as well.

The decay time with the given component values is around 15 seconds before the display could stop at a final random number. The circuit comprises clock oscillator built around NE555 timer IC4, three-stage clock pulse counter built using three CD4033 ICs (IC1 to IC3), and three 7-segment LED displays (DIS1 to DIS3).

In clock oscillator circuit, NE555 timer IC4 is used in a similar way as a free-running astable multivibrator, the only difference being the additional capacitor C1 introduced between pin No. 7 of IC4 and junction of resistors R22 and R24. When toggle switch S1 is in run` position, both terminals of capacitor C1 are shorted by switch S1 and timer IC4 works as a free-running astable multivibrator.

The operating frequency is in the vicinity of 35 kHz, determined by the value of timing components. When toggle switch S1 is flipped from run` to stop` position, capacitor C1 is introduced in the discharge path of pin No. 7 of IC4 and junction of resistors R22 and R24. At the same time, capacitor C4 comes in parallel with timing capacitor C3 to change the operating frequency of the astable from around 35 kHz to around 65 Hz.

Now capacitor C1 slowly starts charging as it is connected in the discharge path of the timing capacitors C3 and C4. The clock frequency of IC4 gradually reduces and after 15 seconds, when capacitor C1 is sufficiently charged, the oscillating frequency gradually drops and finally it stops oscillating.

Thus, pin 3 of IC4 becomes low. Second part of the circuit comprises three cascaded ICs, IC1 through IC3 (CD4033 decade upcounter cum 7-segment decoder). In conjunction with three 7-segment displays (DIS1 to DIS3), these form a 3-digit clock counter. The clock counting speed is dependant upon the clock pulse frequency of IC4. It is connected to clock input pin 1 of IC1 while chip enable pin 2 of IC1 to IC3 are held low. Thus all clock counter ICs advance by 1 for every positive clock transition. Reset pin 15 of all counter ICs is held low through resistor R25. Thus reset facility is not used in this circuit. Due to persistence of vision, one can not distinguish 0-9 counting in DIS1 to DIS3 when the clock frequency is high.

All 7-segment displays appear to show digit 8, while the red LED1 remains lit continuously, indicating clock counter is in running condition. On sliding toggle switch S1 from run` to stop` position, the counting speed of individual digits falls immediately due to the clock frequency changing to around 65 Hz.

Now, the counting speed will be 65 Hz for DIS3, 6. 5 Hz for DIS2, and 0. 6 Hz for DIS1. This speed of individual digit counting slowly decays, until the counter stops and LED1 stops blinking, and the final count (random numbers) are displayed in DIS1, DIS2, and DIS3. 🔗 External reference