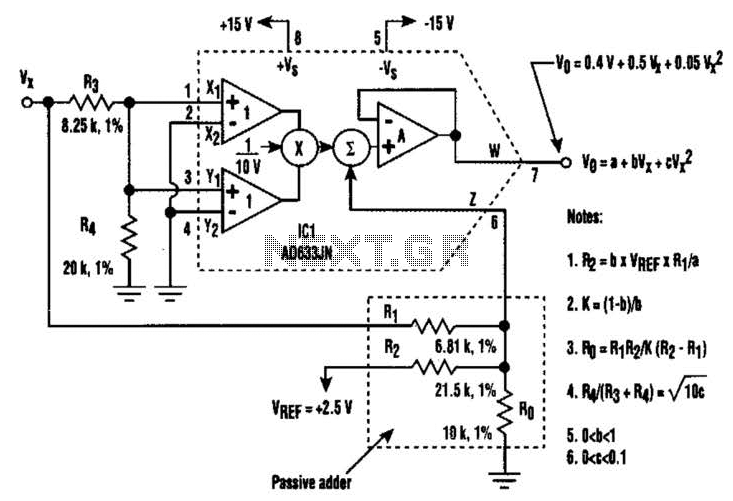

Second-Order Polynomial Generator Circuit

A circuit utilizing a single analog multiplier and five precision resistors can produce an output voltage (Ko) that represents a second-order polynomial. This circuit implements the quadratic function. The input terminals of IC1 are configured to create a positive square term and deliver the Vr signal to the output with a scale factor of 1-10 V. The inclusion of a voltage-divider network (resistors R3 and R4) in the input signal path allows for additional attenuation adjustment of the coefficient (c) of the square term in the quadratic. Furthermore, a passive adder (resistors R1, R2, and R0) is connected to IC1's internal summing circuit to generate the polynomial's other two terms: the offset term (a) and the linear coefficient (b).

The circuit design revolves around the use of an analog multiplier, which serves as the core component for generating the quadratic output. The analog multiplier's functionality allows it to multiply two input voltages, effectively enabling the creation of the square term necessary for the second-order polynomial. The precision resistors play a crucial role in defining the coefficients of the polynomial, ensuring accurate scaling and adjustment of the output voltage.

The input signal, represented by Vr, is processed through a voltage-divider network composed of resistors R3 and R4. This network is essential for managing the input signal's amplitude and adjusting the coefficient (c) associated with the square term. By altering the resistor values, the attenuation can be finely tuned, allowing for precise control over the polynomial's characteristics.

In addition to the square term, the circuit includes a passive adder formed by resistors R1, R2, and R0. This configuration connects to the internal summing circuit of the analog multiplier, enabling the generation of the remaining two polynomial terms: the linear coefficient (b) and the constant offset term (a). The passive adder effectively combines these terms, ensuring that the output voltage accurately reflects the desired second-order polynomial.

Overall, this circuit provides a versatile and precise means of generating second-order polynomial outputs, utilizing a combination of an analog multiplier and carefully selected resistors to achieve the desired electrical characteristics. The design is well-suited for applications requiring polynomial signal generation and can be adapted for various input signal conditions by adjusting the resistor values accordingly. By using a circuit built with a single analog multiplier and five precision resistors, an output voltage (Ko) can be made to create a second- order polynomial. The circuit implements the quadratic shown. The input terminals of IC1 are connected to create a positive square term and present the Vr signal to the output with a 1-10-V scale factor.

Incorporating the voltage-divider network (resistors R3 and R4) in the input signal path provides additional attenuation adjustment for the coefficient (c) of the square term in the quadratic. Then, the passive adder (resistors Rl, R2, and Ro) is wired to ICl`s internal summing circuit to generate the polynomial`s other two terms; the offset term (a) and the linear coefficient (b). 🔗 External reference

The circuit design revolves around the use of an analog multiplier, which serves as the core component for generating the quadratic output. The analog multiplier's functionality allows it to multiply two input voltages, effectively enabling the creation of the square term necessary for the second-order polynomial. The precision resistors play a crucial role in defining the coefficients of the polynomial, ensuring accurate scaling and adjustment of the output voltage.

The input signal, represented by Vr, is processed through a voltage-divider network composed of resistors R3 and R4. This network is essential for managing the input signal's amplitude and adjusting the coefficient (c) associated with the square term. By altering the resistor values, the attenuation can be finely tuned, allowing for precise control over the polynomial's characteristics.

In addition to the square term, the circuit includes a passive adder formed by resistors R1, R2, and R0. This configuration connects to the internal summing circuit of the analog multiplier, enabling the generation of the remaining two polynomial terms: the linear coefficient (b) and the constant offset term (a). The passive adder effectively combines these terms, ensuring that the output voltage accurately reflects the desired second-order polynomial.

Overall, this circuit provides a versatile and precise means of generating second-order polynomial outputs, utilizing a combination of an analog multiplier and carefully selected resistors to achieve the desired electrical characteristics. The design is well-suited for applications requiring polynomial signal generation and can be adapted for various input signal conditions by adjusting the resistor values accordingly. By using a circuit built with a single analog multiplier and five precision resistors, an output voltage (Ko) can be made to create a second- order polynomial. The circuit implements the quadratic shown. The input terminals of IC1 are connected to create a positive square term and present the Vr signal to the output with a 1-10-V scale factor.

Incorporating the voltage-divider network (resistors R3 and R4) in the input signal path provides additional attenuation adjustment for the coefficient (c) of the square term in the quadratic. Then, the passive adder (resistors Rl, R2, and Ro) is wired to ICl`s internal summing circuit to generate the polynomial`s other two terms; the offset term (a) and the linear coefficient (b). 🔗 External reference