Sensitive frequency demodulator LM565 LM111

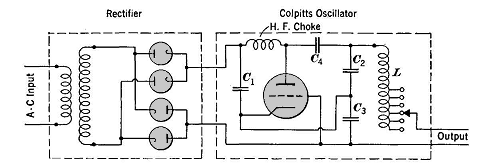

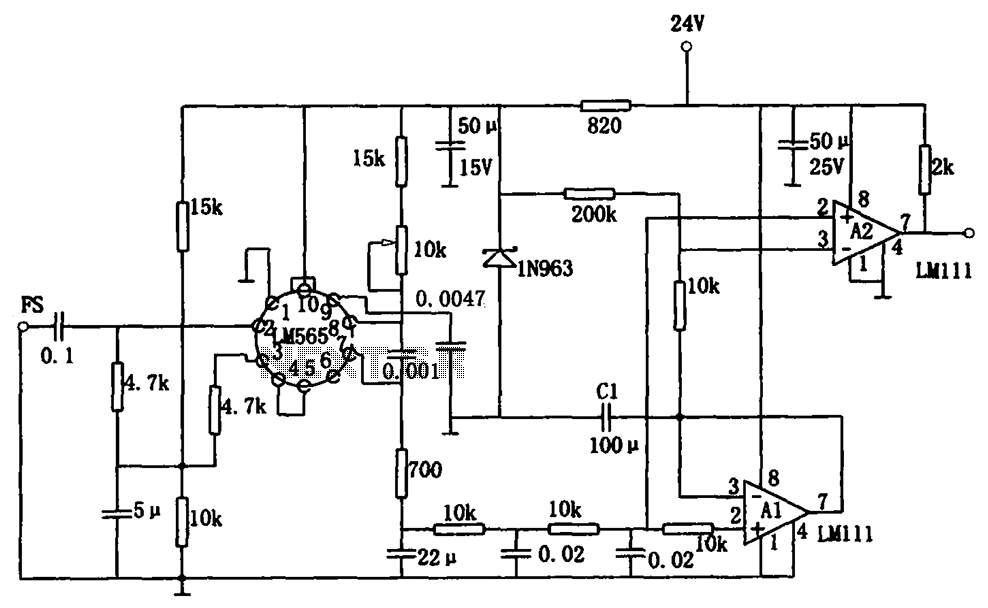

The sensitive frequency demodulation circuit utilizes the LM565 integrated circuit in a phase-locked configuration, allowing it to track frequency offsets across a wide range. However, at small frequency offsets, the signal can produce a minimal demodulated output, causing the voltage-controlled oscillator to drift. This drift leads to an operating point shift in the comparator, resulting in errors. To address these issues, the circuit incorporates a DC regeneration section that enables stable operation even with small deviation signals. The demodulation circuit is fundamentally similar to general frequency demodulation circuits using the LM565 and the LM111 comparator. The key distinction lies in the A2 pin input signal, which is sourced from the peak hold circuit at A1 rather than directly from the LM565. During the FM input signal interval, the output from A1 is low, allowing capacitor C1 to discharge through A1's low output impedance and maintain the peak hold signal. This regenerative approach effectively compensates for voltage-controlled oscillator drift, ensuring that the output from the peak hold circuit remains trackable, thus allowing the comparator to function correctly.

The sensitive frequency demodulation circuit is designed to provide reliable performance even in challenging conditions where frequency offsets are minimal. The use of the LM565 IC in a phase-locked loop configuration enables the circuit to lock onto the input frequency and track variations effectively. The addition of the DC regeneration section is crucial for maintaining the integrity of the demodulated signal, especially when the output signal is weak.

In this circuit, the LM111 comparator plays a vital role in comparing the demodulated output signal against a reference voltage to determine the presence of frequency deviations. The unique configuration where the input to pin A2 is derived from the peak hold circuit at A1 allows for improved stability. This design ensures that even when the output signal from the demodulator is low, the capacitor C1 can discharge effectively, maintaining a consistent voltage level that the comparator can use for accurate frequency detection.

The peak hold circuit is essential for capturing the maximum value of the demodulated signal during the modulation interval, which is then used to inform the comparator of the signal state. The low output impedance of A1 ensures that the peak hold circuit can quickly respond to changes in the input signal, thus enhancing the overall responsiveness of the demodulation circuit.

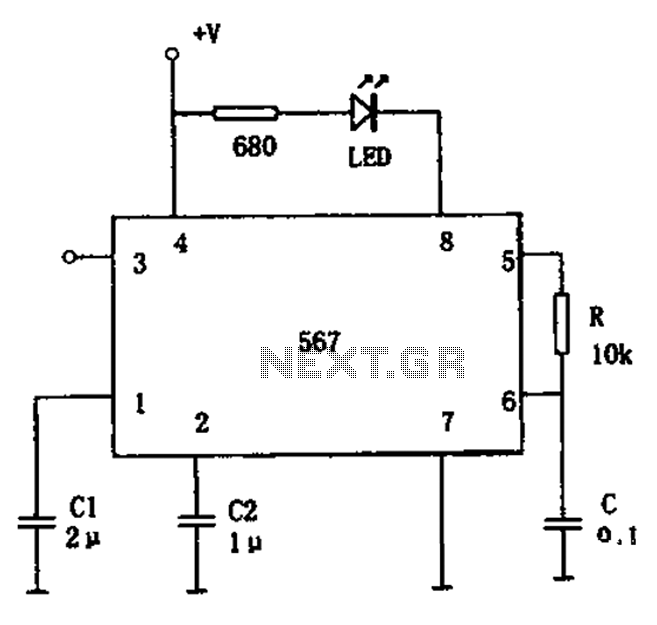

In summary, the sensitive frequency demodulation circuit with LM565 and LM111 components is engineered to deliver precise frequency tracking capabilities while mitigating the effects of signal drift and ensuring stable operation under varying input conditions. This robustness makes it suitable for applications requiring high fidelity in frequency demodulation, such as communication systems and signal processing tasks. As shown for the sensitive frequency demodulation circuit. The circuit uses IC LM565 phase-locked configuration, can track the frequency offset over a wide frequency range. How ever, at small offsets the signal, due to the small demodulated output signal, the voltage controlled oscillator will drift a drift of the operating point of the comparator generates an error. This circuit is to overcome the above drawbacks, the circuit plus a DC regeneration section, which can stably work for a small deviation signal.

FIG, the demodulation circuit and general frequency demodulation circuit LM565 and LM111 comparator constituted substantially the same. The difference is that this circuit A2 pin input signal is not removed from the LM565 feet, but was removed from the peak hold circuit A1.

During the interval of the FM input signal, the output of A1 is low, thus holding the capacitor C1 is discharged A1 low output impedance, and the peak hold signal. With this direct approach to regeneration, despite the presence of a voltage controlled oscillator drift, but the peak hold circuit output can be tracked, so that the comparator can work.

The sensitive frequency demodulation circuit is designed to provide reliable performance even in challenging conditions where frequency offsets are minimal. The use of the LM565 IC in a phase-locked loop configuration enables the circuit to lock onto the input frequency and track variations effectively. The addition of the DC regeneration section is crucial for maintaining the integrity of the demodulated signal, especially when the output signal is weak.

In this circuit, the LM111 comparator plays a vital role in comparing the demodulated output signal against a reference voltage to determine the presence of frequency deviations. The unique configuration where the input to pin A2 is derived from the peak hold circuit at A1 allows for improved stability. This design ensures that even when the output signal from the demodulator is low, the capacitor C1 can discharge effectively, maintaining a consistent voltage level that the comparator can use for accurate frequency detection.

The peak hold circuit is essential for capturing the maximum value of the demodulated signal during the modulation interval, which is then used to inform the comparator of the signal state. The low output impedance of A1 ensures that the peak hold circuit can quickly respond to changes in the input signal, thus enhancing the overall responsiveness of the demodulation circuit.

In summary, the sensitive frequency demodulation circuit with LM565 and LM111 components is engineered to deliver precise frequency tracking capabilities while mitigating the effects of signal drift and ensuring stable operation under varying input conditions. This robustness makes it suitable for applications requiring high fidelity in frequency demodulation, such as communication systems and signal processing tasks. As shown for the sensitive frequency demodulation circuit. The circuit uses IC LM565 phase-locked configuration, can track the frequency offset over a wide frequency range. How ever, at small offsets the signal, due to the small demodulated output signal, the voltage controlled oscillator will drift a drift of the operating point of the comparator generates an error. This circuit is to overcome the above drawbacks, the circuit plus a DC regeneration section, which can stably work for a small deviation signal.

FIG, the demodulation circuit and general frequency demodulation circuit LM565 and LM111 comparator constituted substantially the same. The difference is that this circuit A2 pin input signal is not removed from the LM565 feet, but was removed from the peak hold circuit A1.

During the interval of the FM input signal, the output of A1 is low, thus holding the capacitor C1 is discharged A1 low output impedance, and the peak hold signal. With this direct approach to regeneration, despite the presence of a voltage controlled oscillator drift, but the peak hold circuit output can be tracked, so that the comparator can work.