Solid State Switch for magnet DC Generator

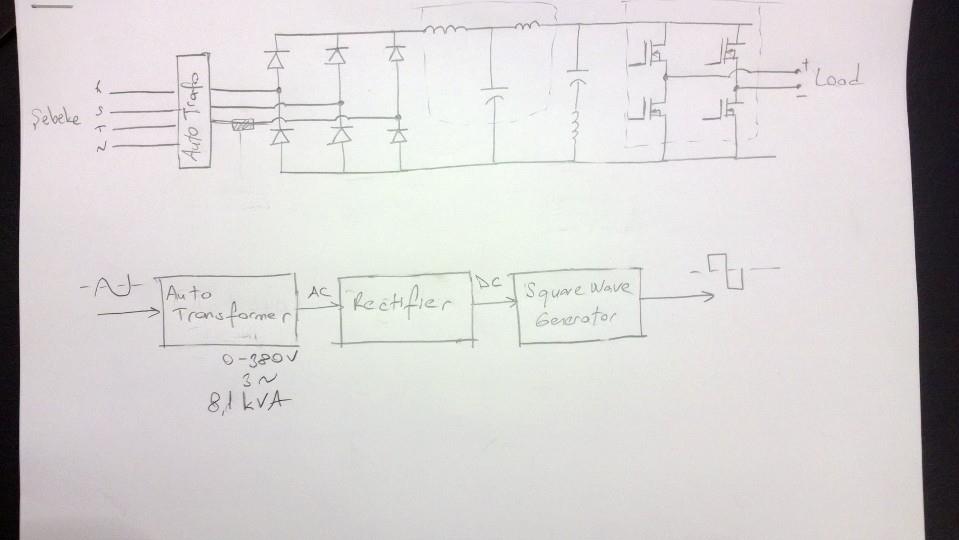

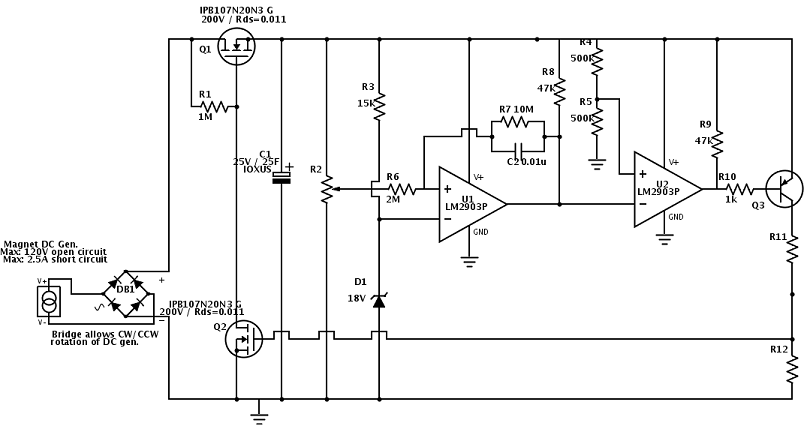

A flywheel-driven permanent magnet DC generator is used to charge a bank of supercapacitors rated at 35 farads and 25V. The maximum charge voltage is limited to 22V using a comparator and a zener reference due to the absence of a stable reference voltage in the system. The generator outputs 120V open-circuit and 2.5A short-circuit at maximum RPM. When charging the capacitor bank from zero volts, a current of 2.5A flows into the bank, causing the voltage to rise. Once the voltage reaches 22V, comparator U1 activates, and U2 inverts this signal to turn on PNP transistor Q3. The intention is to use the signal from Q3's collector to control a switch that disconnects the charging current from the DC generator, preventing overcharging of the capacitor bank. The configuration of Q1 and Q2 is under consideration for this switching mechanism. Initially, with the capacitor bank at zero volts, Q1 is expected to be on as its gate connects to its drain through a 1M resistor. When Q3 raises Q2's gate voltage to approximately 10V, Q2 is expected to pull down Q1's gate voltage to near ground, effectively stopping the charging current to C1. Feedback from resistors R7 and capacitor C2 ensures that U1 will not toggle back until the voltage drops to around 20V. After charging C1 to 22V, Q1 is anticipated to enter cutoff, while the DC generator stops, resulting in Vds = -22V and Vgs = -22V. Concerns arise regarding the effect of this negative Vds on Q1/Q2, despite the component specifications indicating a Vds rating of 200V and a Vgs rating of +/- 30V. Previous experience with an SSR that burned out due to exceeding its voltage rating when the generator's open-circuit voltage reached 120V has heightened caution. When the capacitor bank C1 is fully discharged, it presents a significant load to the generator. The absence of Rs1 resulted in Vaa not exceeding approximately 8V at full RPM, preventing Q1 from fully turning on and causing excessive heat generation. To mitigate this, a large heat sink is currently employed, though the design aims to avoid such high temperatures. The addition of Rs1, a 3-ohm power resistor, allows Vaa to rise to around 17V at generator speed, enabling Q1 to turn on fully. However, this resistor limits the current available to the capacitor bank, doubling the charge time from 0V to 5V. A diode, D3, has been added to counteract Q1's built-in body diode, with uncertainty about its necessity. If the capacitor bank voltage is constrained to 22V by U1 and U2 while the generator is stationary, this results in a reverse bias condition for the power PFET. Future testing will involve developing a subcircuit to bypass Rs1 once the capacitor bank reaches a charge level that maintains Vaa above 15V, potentially utilizing another power NFET across the terminals of Rs1.

The circuit employs a flywheel-driven permanent magnet DC generator to efficiently charge a supercapacitor bank. The generator is capable of producing high voltage and current outputs, with safety mechanisms in place to limit the charge voltage to the supercapacitors. The use of a comparator and zener diode provides a reliable method to monitor and control the charging process, ensuring that the supercapacitors do not exceed their rated voltage.

The switching mechanism is critical to the operation of this circuit. The arrangement of Q1 and Q2 is designed to effectively manage the flow of current from the generator to the capacitor bank. The gate control of Q1 through a resistor allows for initial activation when the capacitor bank is at zero volts. As the voltage builds, Q3's activation leads to a change in Q2's state, which in turn influences Q1 to stop charging the capacitors, thus preventing overcharging.

Thermal management is an important consideration in this design, as the components can generate significant heat during operation. The introduction of a power resistor (Rs1) serves to limit the current and protect the circuit from excessive power draw. However, this also results in a trade-off, as it increases the time required to charge the capacitor bank. The addition of a diode (D3) is a precautionary measure to protect against potential reverse voltage conditions that could damage the power MOSFET.

Future enhancements to the circuit may include the implementation of a subcircuit to dynamically manage the load presented by Rs1, optimizing the charging efficiency while maintaining safe operating conditions for all components involved. This approach will ensure that the system operates reliably and efficiently, maximizing the performance of the flywheel-driven generator and the supercapacitor bank.Using a flywheel-driven permanent magnet DC generator to charge up a bank of supercapacitors, 35 farad rated to 25V. For safety I limit the max charge to 22V via a comparator and a zener reference. Because I have no stable reference voltage at all in in this system, I rely on the zener for a reference.

This small generator, at my max. RPM, put s out 120V open-circuit and 2. 5A short-circuit. Charging up from cap bank at zero volts, indeed 2. 5A flows into the cap bank and voltage climbs. When the voltage on the cap bank reaches 22V, comparator U1 goes high. U2 serves to invert this signal and turn on PNP Q3. I want to use the signal at Q3`s collector to drive some kind of switch to disconnect the charging current from the DC generator, in order to avoid over charging the cap bank. My question is on Q1 and Q2, my hypothetical switch. Does this approach make sense Starting from zero volts on the cap, I expect Q1 to be on as its gate is connected to is drain through the 1M resistor.

As soon as Q3 pulls up Q2`s Vg ~ 10V, I expect Q2 to pull down Q1`s Vg to near ground and effectively shut off charging current to C1. Due to feedback R7 & C2, U1 will not flip back again until ~ 20V. Let`s say that after charging C1 to 22V, Q1 goes into cutoff. Also, the DC generator is at a stop, so Vds = -22V Also, Vgs = -22V. I`m not sure if this condition will wreak havoc with Q1/Q2. The part number ( IP8107N20N3 G ) is spec`d for Vds = 200V and Vgs = +/- 30V but I`m not comfortable with that negative Vds on Q1.

Maybe I am going about this switching completely the wrong way. I`ve already burned out an SSR, which used to be in place of Q1, because my amateur experience forgot that when the load is removed from the generator, its open-circuit voltage climbs to 120V and my DC SSR was rated to switch only 60V. - When cap bank C1 is completely discharged, it presents a very large load to the DC permanent magnet generator.

Consequently, when Rs1 was not present, Vaa never climbed above ~8V at full RPM and thus Q1 never turns on fully; Q1 dissipates enough heat to get smoking hot in a few seconds w/o heatsink. I`m getting around this problem for the moment with a very large heat sink; the part will survive 175C but I really don`t want to get anywhere near that hot in the final design.

- Added Rs1, 3 ohm power resistor. With this load in place, Vaa climbs almost immediately to ~17V when generator is at speed. ( Generator is load-dependent & RPM dependent current and voltage source. ) So Q1 turns fully on. But the tradeoff is now Rs1 limits the available current to the cap bank. The charge time has increased for Vbb 0V->5V by about factor of 2. Not nice. - I needed to add D3 to counteract Q1`s built in body diode. I am only 95% sure I need D3, but I didn`t want to risk frying my power mosfet here. If the cap bank voltage Vbb is limited to 22V ( by U1 & U2, working OK ), and the generator is at standstill, that`ll give me -22V looking from Vbb to Vaa, effectively reverse biasing the power PFET. My next test will be to develop a subcircuit to short-out Rs1 once the cap bank reaches a charge level which will keep Vaa > 15V.

At this point I`m thinking another power NFET across Rs1`s terminals. 🔗 External reference

The circuit employs a flywheel-driven permanent magnet DC generator to efficiently charge a supercapacitor bank. The generator is capable of producing high voltage and current outputs, with safety mechanisms in place to limit the charge voltage to the supercapacitors. The use of a comparator and zener diode provides a reliable method to monitor and control the charging process, ensuring that the supercapacitors do not exceed their rated voltage.

The switching mechanism is critical to the operation of this circuit. The arrangement of Q1 and Q2 is designed to effectively manage the flow of current from the generator to the capacitor bank. The gate control of Q1 through a resistor allows for initial activation when the capacitor bank is at zero volts. As the voltage builds, Q3's activation leads to a change in Q2's state, which in turn influences Q1 to stop charging the capacitors, thus preventing overcharging.

Thermal management is an important consideration in this design, as the components can generate significant heat during operation. The introduction of a power resistor (Rs1) serves to limit the current and protect the circuit from excessive power draw. However, this also results in a trade-off, as it increases the time required to charge the capacitor bank. The addition of a diode (D3) is a precautionary measure to protect against potential reverse voltage conditions that could damage the power MOSFET.

Future enhancements to the circuit may include the implementation of a subcircuit to dynamically manage the load presented by Rs1, optimizing the charging efficiency while maintaining safe operating conditions for all components involved. This approach will ensure that the system operates reliably and efficiently, maximizing the performance of the flywheel-driven generator and the supercapacitor bank.Using a flywheel-driven permanent magnet DC generator to charge up a bank of supercapacitors, 35 farad rated to 25V. For safety I limit the max charge to 22V via a comparator and a zener reference. Because I have no stable reference voltage at all in in this system, I rely on the zener for a reference.

This small generator, at my max. RPM, put s out 120V open-circuit and 2. 5A short-circuit. Charging up from cap bank at zero volts, indeed 2. 5A flows into the cap bank and voltage climbs. When the voltage on the cap bank reaches 22V, comparator U1 goes high. U2 serves to invert this signal and turn on PNP Q3. I want to use the signal at Q3`s collector to drive some kind of switch to disconnect the charging current from the DC generator, in order to avoid over charging the cap bank. My question is on Q1 and Q2, my hypothetical switch. Does this approach make sense Starting from zero volts on the cap, I expect Q1 to be on as its gate is connected to is drain through the 1M resistor.

As soon as Q3 pulls up Q2`s Vg ~ 10V, I expect Q2 to pull down Q1`s Vg to near ground and effectively shut off charging current to C1. Due to feedback R7 & C2, U1 will not flip back again until ~ 20V. Let`s say that after charging C1 to 22V, Q1 goes into cutoff. Also, the DC generator is at a stop, so Vds = -22V Also, Vgs = -22V. I`m not sure if this condition will wreak havoc with Q1/Q2. The part number ( IP8107N20N3 G ) is spec`d for Vds = 200V and Vgs = +/- 30V but I`m not comfortable with that negative Vds on Q1.

Maybe I am going about this switching completely the wrong way. I`ve already burned out an SSR, which used to be in place of Q1, because my amateur experience forgot that when the load is removed from the generator, its open-circuit voltage climbs to 120V and my DC SSR was rated to switch only 60V. - When cap bank C1 is completely discharged, it presents a very large load to the DC permanent magnet generator.

Consequently, when Rs1 was not present, Vaa never climbed above ~8V at full RPM and thus Q1 never turns on fully; Q1 dissipates enough heat to get smoking hot in a few seconds w/o heatsink. I`m getting around this problem for the moment with a very large heat sink; the part will survive 175C but I really don`t want to get anywhere near that hot in the final design.

- Added Rs1, 3 ohm power resistor. With this load in place, Vaa climbs almost immediately to ~17V when generator is at speed. ( Generator is load-dependent & RPM dependent current and voltage source. ) So Q1 turns fully on. But the tradeoff is now Rs1 limits the available current to the cap bank. The charge time has increased for Vbb 0V->5V by about factor of 2. Not nice. - I needed to add D3 to counteract Q1`s built in body diode. I am only 95% sure I need D3, but I didn`t want to risk frying my power mosfet here. If the cap bank voltage Vbb is limited to 22V ( by U1 & U2, working OK ), and the generator is at standstill, that`ll give me -22V looking from Vbb to Vaa, effectively reverse biasing the power PFET. My next test will be to develop a subcircuit to short-out Rs1 once the cap bank reaches a charge level which will keep Vaa > 15V.

At this point I`m thinking another power NFET across Rs1`s terminals. 🔗 External reference