USB Live Oscilloscope: ADCV Board

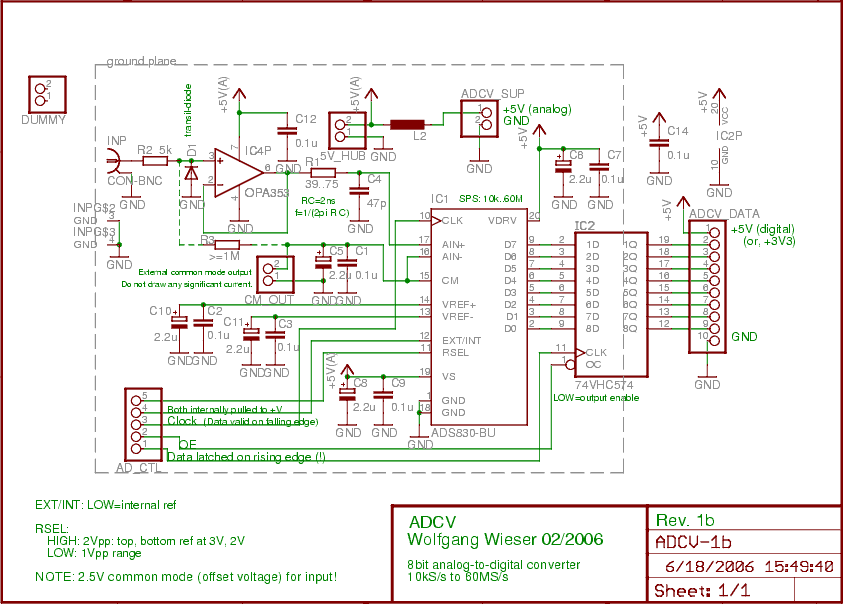

The analog input is initially connected to a fast non-inverting buffer amplifier (OPA353) configured for unity gain, which safeguards the analog-to-digital converter from out-of-range voltages. The ADS830 is an economical 8-bit analog-to-digital converter that accommodates sampling clocks ranging from 10 kS/s to 60 MS/s. It features a 3-stage pipeline, meaning that the conversion result available on the digital outputs corresponds to the analog voltage sampled three clock cycles earlier. With a constant sampling rate of 10 MS/s, this introduces a fixed delay of 300 ns. While this delay is generally inconsequential, it is important to consider when comparing the timing of digital and analog inputs, as the analog signal lags slightly behind. The AD_CTL connector not only supplies the sampling and latch clocks, which share the same frequency but are out of phase, but also provides configuration options for the AD converter, allowing the selection of sensitivity to 1 Vpp or 2 Vpp and the choice between internal and external reference voltages. Currently, there is no dedicated connector for an external reference. The analog input must be connected to the CON-BNC connector. It is crucial to note that the input is DC coupled and requires a common mode offset voltage of 2.5 V. This setup is optimal for 5V single-supply amplifier circuits that operate symmetrically around 2.5 V. However, this may not align with expectations when interfacing with a conventional oscilloscope. If different signal levels are necessary, an additional input amplifier and level shifter will need to be constructed, likely requiring an external power supply.

The circuit design incorporates a fast non-inverting buffer amplifier (OPA353) that serves to protect the analog-to-digital converter (ADC) from potential overvoltage conditions. By operating in a unity gain configuration, the buffer ensures that the signal integrity is maintained while preventing excessive voltage levels from reaching the ADC, thereby safeguarding its functionality.

The ADS830 ADC is selected for its cost-effectiveness and capability to handle a wide range of sampling frequencies, from 10 kS/s to 60 MS/s. Its 3-stage pipeline architecture allows for efficient processing of incoming analog signals, with the output data reflecting the sampled analog voltage from three clock cycles prior. This design choice results in a fixed delay of 300 ns when operating at a sampling rate of 10 MS/s, which is critical for timing analysis in applications where synchronization of digital and analog signals is necessary.

The AD_CTL connector plays a pivotal role in the operation of the ADC by providing both the sampling and latch clocks necessary for the conversion process. The clocks operate at the same frequency but are phase-shifted, ensuring that the ADC functions correctly during the sampling process. Additionally, the configuration options available through this connector allow for flexibility in the system design, enabling adjustments in sensitivity and reference voltage selection to accommodate various signal conditions.

The requirement for a common mode offset voltage of 2.5 V is essential for the proper functioning of the circuit, particularly in systems designed for single-supply operation. This voltage level is optimal for ensuring that the analog signals are processed correctly without distortion or clipping. When connecting to the CON-BNC connector, it is imperative to maintain this offset, as failure to do so may result in inaccurate readings or signal integrity issues.

In scenarios where different signal levels are needed, the design must include additional components, such as an input amplifier and level shifter. This enhancement will likely necessitate an external power supply to accommodate the required voltage levels, ensuring compatibility with various signal sources and measurement instruments. Overall, the described circuit design effectively balances performance, cost, and flexibility, making it suitable for a range of applications in analog signal processing.The analog input is first fed into a fast non-inverting buffer amplifier (OPA353) set up for unity gain which protects the analog-to-digital converter from out-of-range voltages. The ADS830 is a fairly cheap 8-bit analog-to-digital converter which supports sampling clocks from 10kS/s to 60MS/s.

It has sort of a 3-stage pipeline meaning that the co nversion result available on the digital outputs corresponds to the analog voltage 3 clocks earlier. Since we`re sampling on a constant 10MS/s rate (remember: for lower "sampling rates", the sampling clock is still 10MHz but we select only certain samples before committing them to the USB-FX2 FIFO) this introduces a constant delay of 300ns. This is nothing to worry about most of the time but when comparing the time from digital and analog inputs, it must be remembered that the analog signal lags somewhat behind.

The AD_CTL plug not only provides the sampling and latch clocks (they have the same frequency but opposite phase) but also the config for the AD converter allowing to set the sensitivity to 1Vpp or 2Vpp or choosing between internal and external reference. (There is currently no extra plug for an external reference. ) The analog has to be attached to the CON-BNC connector. It must be understood that the input is DC coupled and demands a common mode offset voltage of 2. 5V. This is ideal for 5V single-supply amplifier circuits which operator symmetrically around 2. 5V. However, this is not what one expects when connecting to a "real" oscilloscope. If different signal levels are required, an extra input amplifier and level shifter has to be built (which will probably require an external power supply!).

🔗 External reference

The circuit design incorporates a fast non-inverting buffer amplifier (OPA353) that serves to protect the analog-to-digital converter (ADC) from potential overvoltage conditions. By operating in a unity gain configuration, the buffer ensures that the signal integrity is maintained while preventing excessive voltage levels from reaching the ADC, thereby safeguarding its functionality.

The ADS830 ADC is selected for its cost-effectiveness and capability to handle a wide range of sampling frequencies, from 10 kS/s to 60 MS/s. Its 3-stage pipeline architecture allows for efficient processing of incoming analog signals, with the output data reflecting the sampled analog voltage from three clock cycles prior. This design choice results in a fixed delay of 300 ns when operating at a sampling rate of 10 MS/s, which is critical for timing analysis in applications where synchronization of digital and analog signals is necessary.

The AD_CTL connector plays a pivotal role in the operation of the ADC by providing both the sampling and latch clocks necessary for the conversion process. The clocks operate at the same frequency but are phase-shifted, ensuring that the ADC functions correctly during the sampling process. Additionally, the configuration options available through this connector allow for flexibility in the system design, enabling adjustments in sensitivity and reference voltage selection to accommodate various signal conditions.

The requirement for a common mode offset voltage of 2.5 V is essential for the proper functioning of the circuit, particularly in systems designed for single-supply operation. This voltage level is optimal for ensuring that the analog signals are processed correctly without distortion or clipping. When connecting to the CON-BNC connector, it is imperative to maintain this offset, as failure to do so may result in inaccurate readings or signal integrity issues.

In scenarios where different signal levels are needed, the design must include additional components, such as an input amplifier and level shifter. This enhancement will likely necessitate an external power supply to accommodate the required voltage levels, ensuring compatibility with various signal sources and measurement instruments. Overall, the described circuit design effectively balances performance, cost, and flexibility, making it suitable for a range of applications in analog signal processing.The analog input is first fed into a fast non-inverting buffer amplifier (OPA353) set up for unity gain which protects the analog-to-digital converter from out-of-range voltages. The ADS830 is a fairly cheap 8-bit analog-to-digital converter which supports sampling clocks from 10kS/s to 60MS/s.

It has sort of a 3-stage pipeline meaning that the co nversion result available on the digital outputs corresponds to the analog voltage 3 clocks earlier. Since we`re sampling on a constant 10MS/s rate (remember: for lower "sampling rates", the sampling clock is still 10MHz but we select only certain samples before committing them to the USB-FX2 FIFO) this introduces a constant delay of 300ns. This is nothing to worry about most of the time but when comparing the time from digital and analog inputs, it must be remembered that the analog signal lags somewhat behind.

The AD_CTL plug not only provides the sampling and latch clocks (they have the same frequency but opposite phase) but also the config for the AD converter allowing to set the sensitivity to 1Vpp or 2Vpp or choosing between internal and external reference. (There is currently no extra plug for an external reference. ) The analog has to be attached to the CON-BNC connector. It must be understood that the input is DC coupled and demands a common mode offset voltage of 2. 5V. This is ideal for 5V single-supply amplifier circuits which operator symmetrically around 2. 5V. However, this is not what one expects when connecting to a "real" oscilloscope. If different signal levels are required, an extra input amplifier and level shifter has to be built (which will probably require an external power supply!).

🔗 External reference

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713