USB Live Oscilloscope: Main Board

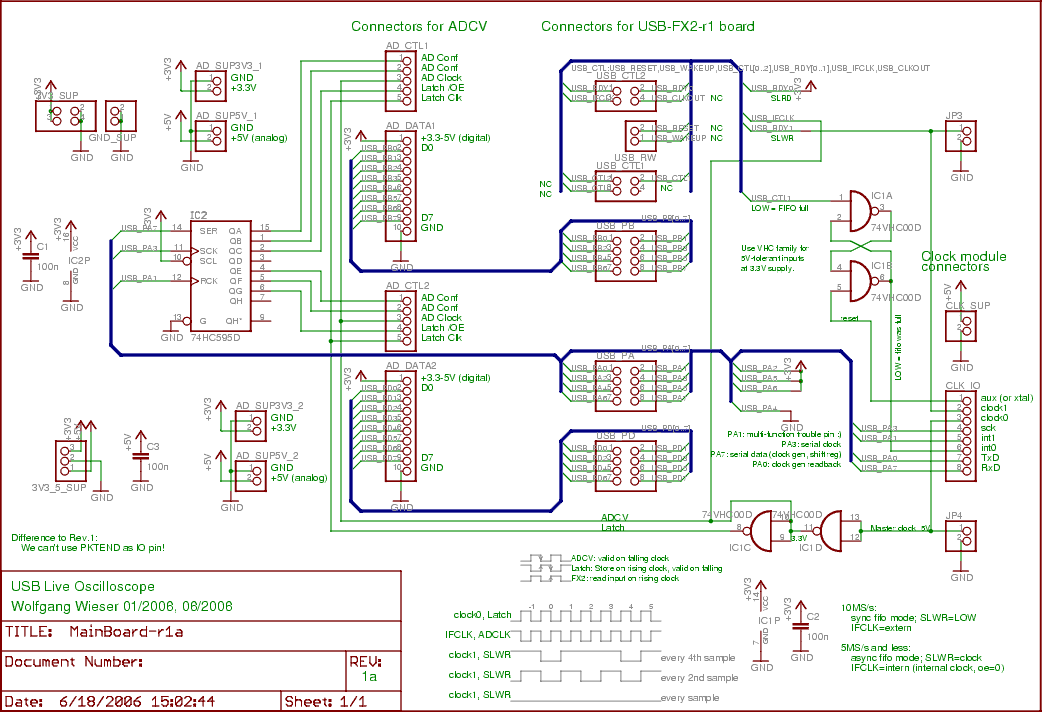

The two input boards (ADCV or digital) are connected to AD_CTL1, AD_DATA1, AD_SUP5V_1, and AD_SUP3V3_1 for the first board, with the second board using the same connections but with a suffix of 2. To transfer sampling data, the 16 digital data lines from the two input boards are routed into the 16-bit wide bus of the FX2-USB board (USB_PA). Each input board can support up to three control lines (pins 1, 2, and 4 of AD_CTL), which are controlled by the USB-FX2 board's 8051 controller through lines USB_PA1, 3, 7, and a shift register (IC2). IC1A and IC1B form an RS flip-flop designed to detect FIFO buffer overflows, indicating when the USB-FX2 board cannot transmit data over USB quickly enough. This flip-flop is linked to the clock generator to enable response actions. However, this feature is currently unused, and FIFO stalls could likely be detected via a software interrupt in the FX2. IC1C and IC1D are responsible for clock inversion since the ADCV clock and interface clock need to be inverted relative to the latch clock. Refer to the waveform diagrams in the schematic for further details.

The circuit incorporates two input boards, either ADCV or digital, facilitating data acquisition through dedicated connections to the FX2-USB interface. The first board utilizes the labels AD_CTL1, AD_DATA1, AD_SUP5V_1, and AD_SUP3V3_1, while the second board mirrors these connections with a numerical suffix of 2. The architecture is designed to handle the transmission of 16 digital data lines from both input boards, which are integrated into a 16-bit wide data bus on the FX2-USB board, denoted as USB_PA.

Control signals are essential for the operation of each input board, with a maximum of three control lines available (located at pins 1, 2, and 4 of AD_CTL). These lines are managed by the 8051 microcontroller on the USB-FX2 board, utilizing specific data lines (USB_PA1, USB_PA3, and USB_PA7) along with a shift register (IC2) to facilitate control signal management.

The design includes an RS flip-flop configuration formed by IC1A and IC1B, intended to monitor FIFO buffer performance. This component plays a critical role in identifying conditions where data transfer rates are insufficient, potentially leading to buffer overflows. The flip-flop is interconnected with a clock generator, allowing it to respond to timing issues; however, it is noted that this feature is not actively utilized in the current setup. Instead, it is suggested that FIFO stalls may be effectively monitored through software interrupts implemented within the FX2 architecture.

Furthermore, the circuit addresses clock signal integrity through the inclusion of IC1C and IC1D, which are tasked with inverting the clock signals. This inversion is necessary to synchronize the ADCV clock and the interface clock with the latch clock, ensuring proper timing across the system. For a clearer understanding of the timing relationships and signal transitions, reference to the waveform diagrams provided in the schematic is recommended.The two input boards ( ADCV or digital ) get connected to AD_CTL1, AD_DATA1, AD_SUP5V_1, AD_SUP3V3_1 for the first board and the same names with suffix 2 for the second board. To transfer the sampling data, the 16 digital data lines from the two input boards are fed into the 16bit wide bus of the FX2-USB board (USB_PA, ).

Each input board can have up to 3 control lines (pins 1, 2 and 4 of AD_CTL) which are set from the USB-FX2 board`s 8051 controller via lines USB_PA1, 3, 7 and shift register IC2. IC1A, B form together an RS-flip-flop which was meant to detect FIFO buffer overflows (i. e. when the USB-FX2 board is not able to transmit data over the USB fast enough). It is connected to the clock generator so that it can take action. However, this feature currently is not used at all and the FIFO stall can probably also be detected by a software interrupt in the FX2.

IC1C, D to the necessary clock inversion because ADCV clock and interface clock need to be inverted compared to the latch clock. (See also the waveform diagrams on the schematic. ) 🔗 External reference

The circuit incorporates two input boards, either ADCV or digital, facilitating data acquisition through dedicated connections to the FX2-USB interface. The first board utilizes the labels AD_CTL1, AD_DATA1, AD_SUP5V_1, and AD_SUP3V3_1, while the second board mirrors these connections with a numerical suffix of 2. The architecture is designed to handle the transmission of 16 digital data lines from both input boards, which are integrated into a 16-bit wide data bus on the FX2-USB board, denoted as USB_PA.

Control signals are essential for the operation of each input board, with a maximum of three control lines available (located at pins 1, 2, and 4 of AD_CTL). These lines are managed by the 8051 microcontroller on the USB-FX2 board, utilizing specific data lines (USB_PA1, USB_PA3, and USB_PA7) along with a shift register (IC2) to facilitate control signal management.

The design includes an RS flip-flop configuration formed by IC1A and IC1B, intended to monitor FIFO buffer performance. This component plays a critical role in identifying conditions where data transfer rates are insufficient, potentially leading to buffer overflows. The flip-flop is interconnected with a clock generator, allowing it to respond to timing issues; however, it is noted that this feature is not actively utilized in the current setup. Instead, it is suggested that FIFO stalls may be effectively monitored through software interrupts implemented within the FX2 architecture.

Furthermore, the circuit addresses clock signal integrity through the inclusion of IC1C and IC1D, which are tasked with inverting the clock signals. This inversion is necessary to synchronize the ADCV clock and the interface clock with the latch clock, ensuring proper timing across the system. For a clearer understanding of the timing relationships and signal transitions, reference to the waveform diagrams provided in the schematic is recommended.The two input boards ( ADCV or digital ) get connected to AD_CTL1, AD_DATA1, AD_SUP5V_1, AD_SUP3V3_1 for the first board and the same names with suffix 2 for the second board. To transfer the sampling data, the 16 digital data lines from the two input boards are fed into the 16bit wide bus of the FX2-USB board (USB_PA, ).

Each input board can have up to 3 control lines (pins 1, 2 and 4 of AD_CTL) which are set from the USB-FX2 board`s 8051 controller via lines USB_PA1, 3, 7 and shift register IC2. IC1A, B form together an RS-flip-flop which was meant to detect FIFO buffer overflows (i. e. when the USB-FX2 board is not able to transmit data over the USB fast enough). It is connected to the clock generator so that it can take action. However, this feature currently is not used at all and the FIFO stall can probably also be detected by a software interrupt in the FX2.

IC1C, D to the necessary clock inversion because ADCV clock and interface clock need to be inverted compared to the latch clock. (See also the waveform diagrams on the schematic. ) 🔗 External reference