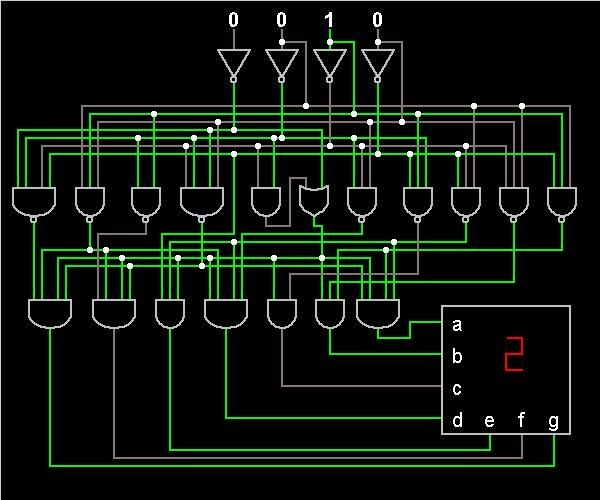

7-Segment LED Decoder

It is possible to implement a circuit using both P-MOS and N-MOS transistors, referred to as CMOS technology. In this context, a three-terminal NAND gate can be constructed. This gate is classified as a universal gate, widely utilized in various applications, allowing for further development.

The CMOS (Complementary Metal-Oxide-Semiconductor) technology combines P-MOS and N-MOS transistors to create efficient and versatile digital logic circuits. The three-terminal NAND gate is a fundamental building block in digital electronics, characterized by its ability to perform the NAND operation, which outputs a low signal only when all inputs are high.

In the construction of a three-terminal NAND gate using CMOS technology, two N-MOS transistors are connected in series between the output and ground, while two P-MOS transistors are connected in parallel between the output and the power supply. The gates of these transistors are connected to the input terminals. When both inputs are high (logic '1'), the N-MOS transistors conduct, creating a path to ground and pulling the output low (logic '0'). Conversely, when at least one input is low (logic '0'), the P-MOS transistors will conduct, allowing the output to be pulled high (logic '1').

The advantages of using CMOS technology for NAND gates include low static power consumption, high noise immunity, and the ability to integrate a large number of transistors on a single chip, making it suitable for modern digital circuits, including microprocessors and memory devices. The universal nature of the NAND gate allows it to be used to construct any other logic gate, thus serving as a cornerstone in digital circuit design.It can be possible and it can be implemented using P-MOS and N-MOS together in a circuit i. e. what is called C-MOS. There we can implement Three Terminal NAND GATE. It is a universal gate which is used commonly so can proceed further. 🔗 External reference

The CMOS (Complementary Metal-Oxide-Semiconductor) technology combines P-MOS and N-MOS transistors to create efficient and versatile digital logic circuits. The three-terminal NAND gate is a fundamental building block in digital electronics, characterized by its ability to perform the NAND operation, which outputs a low signal only when all inputs are high.

In the construction of a three-terminal NAND gate using CMOS technology, two N-MOS transistors are connected in series between the output and ground, while two P-MOS transistors are connected in parallel between the output and the power supply. The gates of these transistors are connected to the input terminals. When both inputs are high (logic '1'), the N-MOS transistors conduct, creating a path to ground and pulling the output low (logic '0'). Conversely, when at least one input is low (logic '0'), the P-MOS transistors will conduct, allowing the output to be pulled high (logic '1').

The advantages of using CMOS technology for NAND gates include low static power consumption, high noise immunity, and the ability to integrate a large number of transistors on a single chip, making it suitable for modern digital circuits, including microprocessors and memory devices. The universal nature of the NAND gate allows it to be used to construct any other logic gate, thus serving as a cornerstone in digital circuit design.It can be possible and it can be implemented using P-MOS and N-MOS together in a circuit i. e. what is called C-MOS. There we can implement Three Terminal NAND GATE. It is a universal gate which is used commonly so can proceed further. 🔗 External reference