Inductor saturation tester alternative route to dump the excess energy

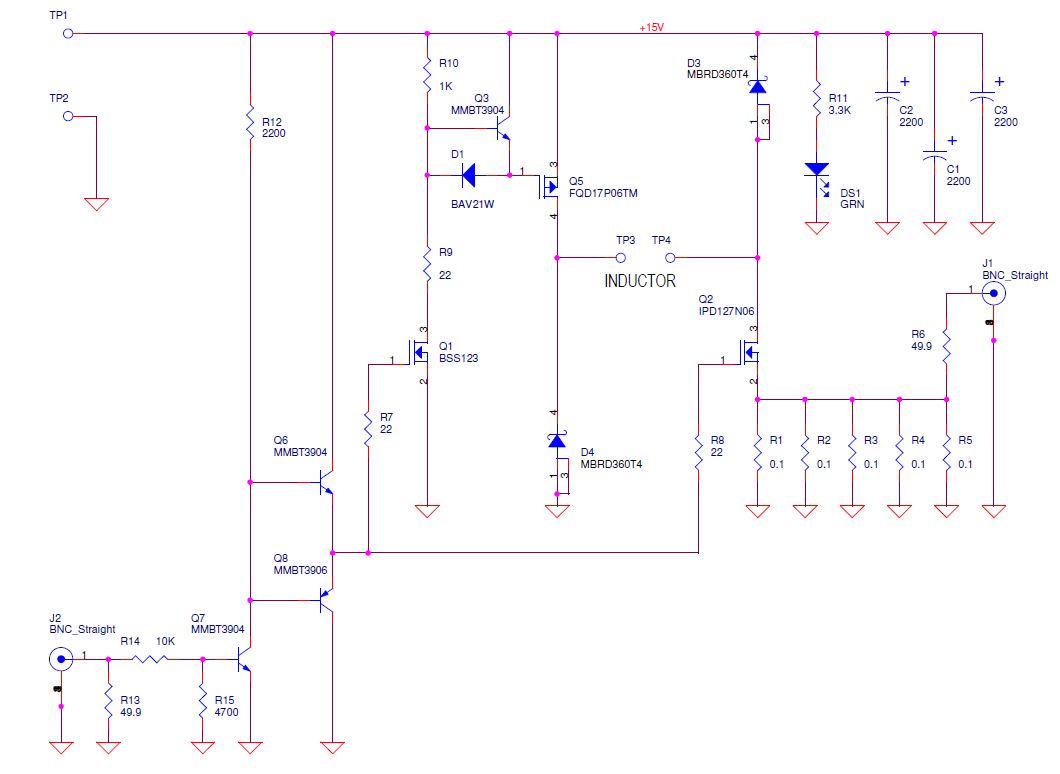

Yes, it does charge the inductor again. Diodes are beneficial as they do not charge the inductor back but dissipate a significant amount of instantaneous power due to the forward voltage drop. One approach would be to monitor the current and cease driving the FETs when the current turns negative; however, this solution may be quite complex. A suitable resistor in parallel with the left diode could resolve the charging issue, provided that charging the capacitor is not time-sensitive, meaning the pulse frequency is low enough to allow adequate time for capacitor charging before the next pulse. The intent of initiating this discussion was to learn and to design a simpler version compared to Janne's well-constructed design, where the concept of dissipating excess energy from the inductor emerged during the learning process. The plan is to create a standalone unit where the signal is generated using a simpler PWM generator, such as a 555 timer for producing a triangle wave, and a comparator like the LM311 with a potentiometer for duty cycle adjustment to achieve minimal pulse width at low frequency. This approach should be feasible. The provided oscilloscope images are impressive; if possible, it would be beneficial to shorten the pulse duration to approximately 10 microseconds to approach the "knee" without causing the signal to spike excessively, allowing for a complete cycle to be displayed clearly on the oscilloscope screen. The traces indicate that the inductor's decay rate was rapid. Additionally, inquiries about the discharge cycle during the inductor's energy release are raised. If feasible, tracing the TP4 point would be interesting to observe the voltage fluctuations during the decay phase. Off-topic, the decaying red trace from the TCP202 appears to have a slower slope compared to the vertical black inductor trace; this raises questions about the probe's limitations. The initial image has been zoomed out to illustrate more of the cycle, with the upper trace representing the output from J1. The sharp edge is observed when the MOSFET Q2 is switched off, making it impossible to measure the inductor current. The current draw from the 10V power supply during this test was 0.058A, equating to 0.58W, which encompasses all power consumption within the gate drive circuitry. The inquiry into the inductor's self-dissipation of excess energy during the ringing observed in the oscilloscope shot is noted, alongside curiosity about the percentage of energy remaining during that ringing period. The current draw of 58mA at 10V indicates a low power requirement, suggesting that a robust power supply may not be necessary. This is particularly relevant for inductors with high inductance and high current saturation, which exhibit a slow di/dt or a shallow trace.

The circuit described involves an inductor charging and discharging mechanism, where diodes play a crucial role in preventing back charging of the inductor while managing power dissipation. The use of a resistor in parallel with one of the diodes is proposed to mitigate issues related to charging time, especially when operating at lower pulse frequencies. The design aims to leverage a PWM generator for signal modulation, which simplifies the control mechanism while allowing for effective duty cycle adjustments through a comparator.

In practical applications, monitoring the current through the inductor is essential to optimize performance and prevent damage to the FETs. Implementing a feedback mechanism to halt FET operation when negative current is detected could enhance efficiency, although it may introduce complexity into the design.

The oscilloscope traces provide valuable insights into the operation of the circuit, showcasing the inductor's behavior during charging and discharging phases. The sharp transitions observed in the waveforms are indicative of the rapid changes in current as the MOSFET switches states. The energy dissipation characteristics, particularly during the ringing phase, are critical for understanding the overall efficiency of the circuit.

This design approach emphasizes the importance of careful component selection and configuration to achieve the desired performance metrics while maintaining simplicity in the circuit layout. The choice of a 555 timer for PWM generation and the LM311 for signal comparison reflects a focus on utilizing readily available components to facilitate ease of construction and troubleshooting.

Overall, the circuit demonstrates a balance between complexity and functionality, aiming to create an effective energy management system while fostering an educational environment for further exploration and development in electronic circuit design.Yes, it does charge the inductor again. Diodes are a good that they will not charge the inductor back but of course dissipate fair amount of instantaneous power due to the forward voltage drop. One way would be to monitor the current and stop driving those fets when the current turns negative, but I guess that is quite complex solution.

I think that a suitable resistor in parallel of the left diode will solve that charging problem, provided that you are not in a hurry to charge the capacitor, i. e. the pulse frequency is low enough, so that there is enough time to charge the capacitor before the next pulse.

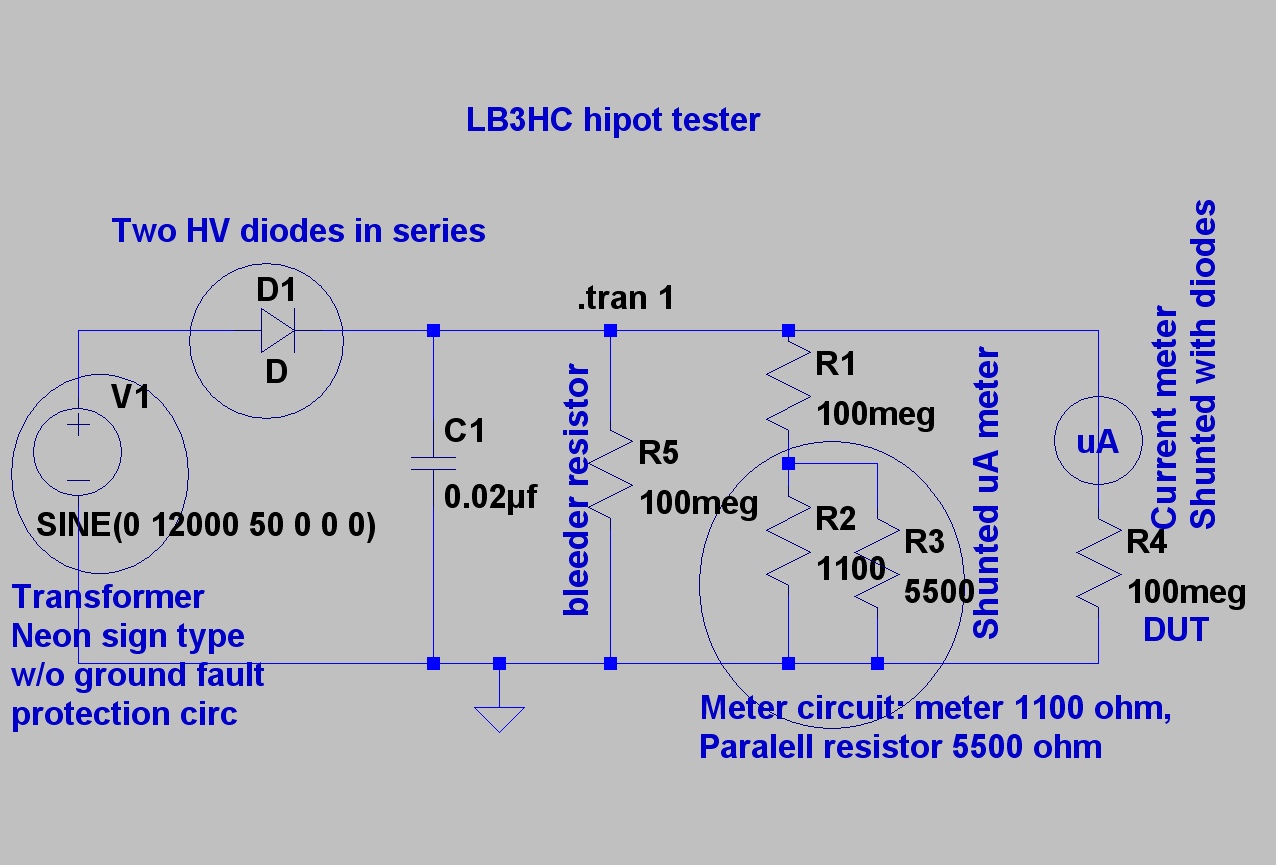

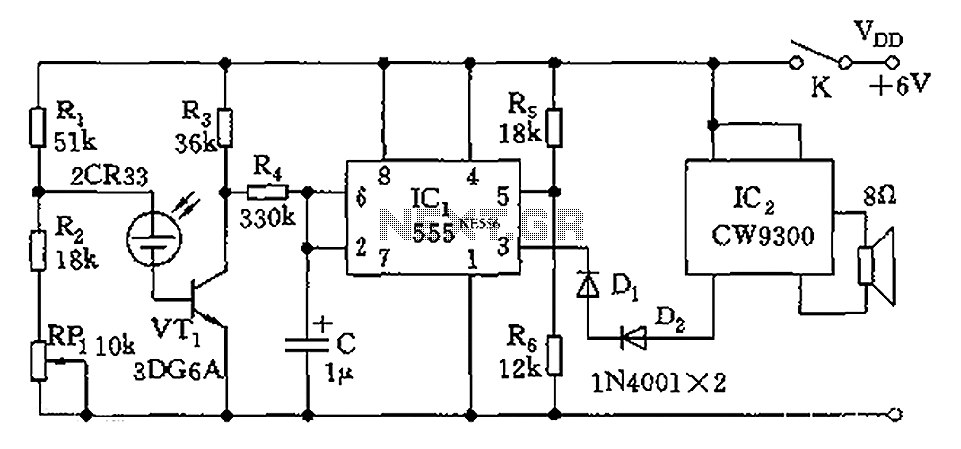

To be honest, the reason I started this thread was to start learning and trying to build much simpler one compared to Janne`s nicely built, and the idea of dissipating the excess energy from the inductor popped out while learning it. In my version, the plan is to build a standalone unit with the signal will be supplied by using a much simpler pwm generator like using a 555 for generating the triangle wave and a comparator maybe like LM311 with a pot for duty cycle adjustment in order to get a really small pulse at low frequency.

This should be workable right Those scope shots are really nice, and if its not too troublesome, please shorten the pulse maybe like 10us to get close to the "knee" without the signal shooting up too high to show the complete cycle nicely in the scope screen. And from your traces, it looks like the inductor decaying speed was so fast. Also how is the discharge cycle when the inductor was releasing the energy Again, if you had a chance, please do trace the TP4 point, curious to see how the voltage jumps at the point during the decay period.

Off topic, your TCP202 decaying red trace is slower with a slope compared to the black inductor trace which is straight vertical, why is that The probe`s limitation In this first picture I have `zoomed out` to show the more of the cycle. The upper trace is the output from J1. The sharp edge is caused when the MOSFET Q2 is turned off, it is no longer possible to measure the inductor current.

The current draw from the 10V power supply from this test was 0. 058A, which is 0. 58W and this includes all the power consumption in the gate drive circuitry. In this first picture I have `zoomed out` to show the more of the cycle. The upper trace is the output from J1. The sharp edge is caused when the MOSFET Q2 is turned off, it is no longer possible to measure the inductor current. During the decaying period, once the inductor`s voltage (minus diodes drop out) is equal to power supply rail, the inductor will self dissipate the rest of it`s own excess energy through the ringing as observed at the scope shot, am I correct Just curious and purely academical here, curious in ball park number on how much percentage of the energy left in percentage of total only at that ringing period The current draw from the 10V power supply from this test was 0.

058A, which is 0. 58W and this includes all the power consumption in the gate drive circuitry. I`m aware of the energy required to charge those big caps when the circuit was turned on for the 1st time, but lets ignore this initial state, from this result that this circuit draws only 58 ma at 10 volt is pretty low isn`t it This is valuable info, so I don`t need a beefy power supply. The reason is, say for an inductor with high inductance and high current saturation, this will have a really slow di/dt or shallow loong trace, so the easier part is to cr

🔗 External reference

The circuit described involves an inductor charging and discharging mechanism, where diodes play a crucial role in preventing back charging of the inductor while managing power dissipation. The use of a resistor in parallel with one of the diodes is proposed to mitigate issues related to charging time, especially when operating at lower pulse frequencies. The design aims to leverage a PWM generator for signal modulation, which simplifies the control mechanism while allowing for effective duty cycle adjustments through a comparator.

In practical applications, monitoring the current through the inductor is essential to optimize performance and prevent damage to the FETs. Implementing a feedback mechanism to halt FET operation when negative current is detected could enhance efficiency, although it may introduce complexity into the design.

The oscilloscope traces provide valuable insights into the operation of the circuit, showcasing the inductor's behavior during charging and discharging phases. The sharp transitions observed in the waveforms are indicative of the rapid changes in current as the MOSFET switches states. The energy dissipation characteristics, particularly during the ringing phase, are critical for understanding the overall efficiency of the circuit.

This design approach emphasizes the importance of careful component selection and configuration to achieve the desired performance metrics while maintaining simplicity in the circuit layout. The choice of a 555 timer for PWM generation and the LM311 for signal comparison reflects a focus on utilizing readily available components to facilitate ease of construction and troubleshooting.

Overall, the circuit demonstrates a balance between complexity and functionality, aiming to create an effective energy management system while fostering an educational environment for further exploration and development in electronic circuit design.Yes, it does charge the inductor again. Diodes are a good that they will not charge the inductor back but of course dissipate fair amount of instantaneous power due to the forward voltage drop. One way would be to monitor the current and stop driving those fets when the current turns negative, but I guess that is quite complex solution.

I think that a suitable resistor in parallel of the left diode will solve that charging problem, provided that you are not in a hurry to charge the capacitor, i. e. the pulse frequency is low enough, so that there is enough time to charge the capacitor before the next pulse.

To be honest, the reason I started this thread was to start learning and trying to build much simpler one compared to Janne`s nicely built, and the idea of dissipating the excess energy from the inductor popped out while learning it. In my version, the plan is to build a standalone unit with the signal will be supplied by using a much simpler pwm generator like using a 555 for generating the triangle wave and a comparator maybe like LM311 with a pot for duty cycle adjustment in order to get a really small pulse at low frequency.

This should be workable right Those scope shots are really nice, and if its not too troublesome, please shorten the pulse maybe like 10us to get close to the "knee" without the signal shooting up too high to show the complete cycle nicely in the scope screen. And from your traces, it looks like the inductor decaying speed was so fast. Also how is the discharge cycle when the inductor was releasing the energy Again, if you had a chance, please do trace the TP4 point, curious to see how the voltage jumps at the point during the decay period.

Off topic, your TCP202 decaying red trace is slower with a slope compared to the black inductor trace which is straight vertical, why is that The probe`s limitation In this first picture I have `zoomed out` to show the more of the cycle. The upper trace is the output from J1. The sharp edge is caused when the MOSFET Q2 is turned off, it is no longer possible to measure the inductor current.

The current draw from the 10V power supply from this test was 0. 058A, which is 0. 58W and this includes all the power consumption in the gate drive circuitry. In this first picture I have `zoomed out` to show the more of the cycle. The upper trace is the output from J1. The sharp edge is caused when the MOSFET Q2 is turned off, it is no longer possible to measure the inductor current. During the decaying period, once the inductor`s voltage (minus diodes drop out) is equal to power supply rail, the inductor will self dissipate the rest of it`s own excess energy through the ringing as observed at the scope shot, am I correct Just curious and purely academical here, curious in ball park number on how much percentage of the energy left in percentage of total only at that ringing period The current draw from the 10V power supply from this test was 0.

058A, which is 0. 58W and this includes all the power consumption in the gate drive circuitry. I`m aware of the energy required to charge those big caps when the circuit was turned on for the 1st time, but lets ignore this initial state, from this result that this circuit draws only 58 ma at 10 volt is pretty low isn`t it This is valuable info, so I don`t need a beefy power supply. The reason is, say for an inductor with high inductance and high current saturation, this will have a really slow di/dt or shallow loong trace, so the easier part is to cr

🔗 External reference