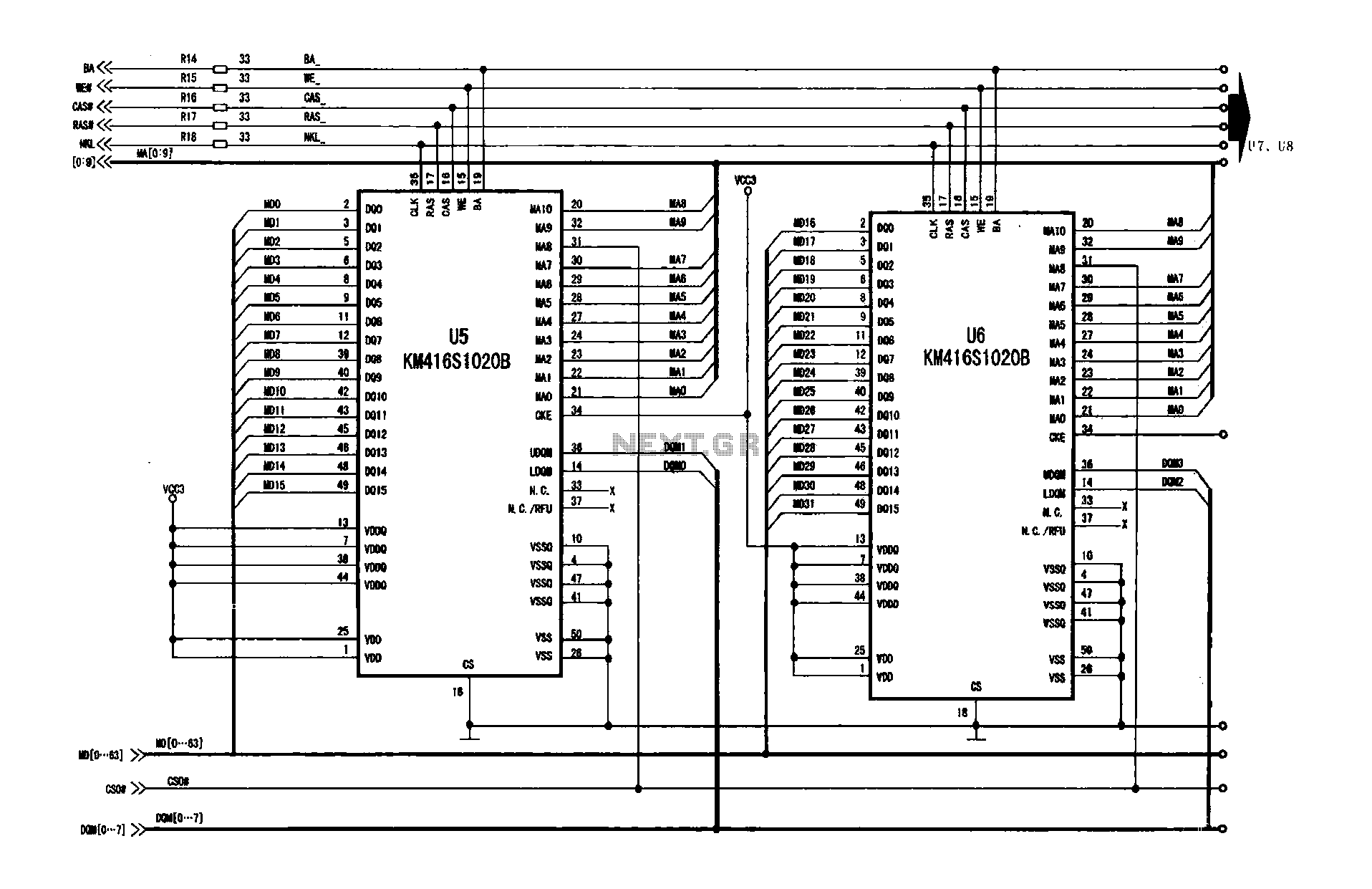

The frame memory circuit

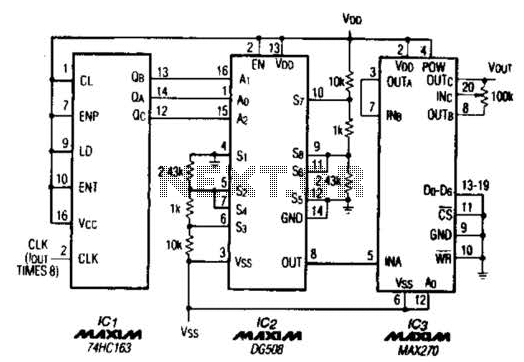

A digital signal processing circuit that operates in conjunction with a memory system for temporarily storing image data. The DPTVT-3D/MV digital processing chip requires four KM416S102 memory units, each providing 16 MB of digital memory. The circuit structure is depicted in Figure 26-6, where only one of the two memory units (U5, U6) is illustrated; the other two (U7, U8) are not represented. Each memory unit features 16 lines for 16-bit parallel data, allowing the DPTVT-3D/MV chip to access a total of 64 data lines. Additionally, each memory unit has 10 address lines connected to the main digital signal processing chip, along with a shared control bus.

The digital signal processing (DSP) circuit is designed to facilitate efficient image data handling through a structured memory architecture. The DPTVT-3D/MV chip serves as the core processing unit, interfacing with four KM416S102 memory chips, each capable of storing 16 MB of data. The arrangement allows for a total of 64 data lines, which enables the DSP to manage large volumes of image data in parallel, enhancing processing speed and efficiency.

The memory units are connected to the DPTVT-3D/MV chip via 16 data lines per unit, facilitating simultaneous data transfer across multiple channels. This parallel configuration is crucial for applications requiring high-speed data processing, such as real-time image analysis or video processing. Each memory unit is also equipped with 10 address lines, which are essential for accessing specific memory locations within the chip. This addressing capability allows the DSP to retrieve and manipulate data efficiently, ensuring that the required information is available when needed.

Furthermore, a common control bus connects all memory units to the main DSP chip, allowing for coordinated control signals to manage read and write operations across the memory modules. This architecture not only streamlines data flow but also simplifies the control logic required for memory management, making the circuit more robust and easier to integrate into larger systems. The overall design emphasizes modularity and scalability, making it suitable for various digital signal processing applications that demand high performance and reliability.Digital signal processing circuit when work needs to cooperate with it with a memory for temporarily storing image data. DPTVT-3D/MV digital processing chip need four KM416S102 0B (16 MB) digital memory and it is coupled, the circuit structure shown in Figure 26-6, only one is drawn out of the two pieces (U5, U6), the remaining two (U7, U8) is not successful in the drawing. Each memory has 16 lines, or 16-bit parallel data and digital processing chip DPTVT-3D/MV is connected to access a data signal, a total of 64 lines.

In addition, each memory has 10 lines (to address signal) is connected to the main digital signal processing chip, in addition to the common control bus

The digital signal processing (DSP) circuit is designed to facilitate efficient image data handling through a structured memory architecture. The DPTVT-3D/MV chip serves as the core processing unit, interfacing with four KM416S102 memory chips, each capable of storing 16 MB of data. The arrangement allows for a total of 64 data lines, which enables the DSP to manage large volumes of image data in parallel, enhancing processing speed and efficiency.

The memory units are connected to the DPTVT-3D/MV chip via 16 data lines per unit, facilitating simultaneous data transfer across multiple channels. This parallel configuration is crucial for applications requiring high-speed data processing, such as real-time image analysis or video processing. Each memory unit is also equipped with 10 address lines, which are essential for accessing specific memory locations within the chip. This addressing capability allows the DSP to retrieve and manipulate data efficiently, ensuring that the required information is available when needed.

Furthermore, a common control bus connects all memory units to the main DSP chip, allowing for coordinated control signals to manage read and write operations across the memory modules. This architecture not only streamlines data flow but also simplifies the control logic required for memory management, making the circuit more robust and easier to integrate into larger systems. The overall design emphasizes modularity and scalability, making it suitable for various digital signal processing applications that demand high performance and reliability.Digital signal processing circuit when work needs to cooperate with it with a memory for temporarily storing image data. DPTVT-3D/MV digital processing chip need four KM416S102 0B (16 MB) digital memory and it is coupled, the circuit structure shown in Figure 26-6, only one is drawn out of the two pieces (U5, U6), the remaining two (U7, U8) is not successful in the drawing. Each memory has 16 lines, or 16-bit parallel data and digital processing chip DPTVT-3D/MV is connected to access a data signal, a total of 64 lines.

In addition, each memory has 10 lines (to address signal) is connected to the main digital signal processing chip, in addition to the common control bus