LAN Tester circuit diagram

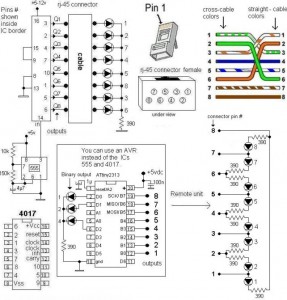

A LAN tester circuit diagram is presented in two designs. The first design utilizes a timer IC 555 and a decade counter 4017. The second design employs a microcontroller ATtiny2313.

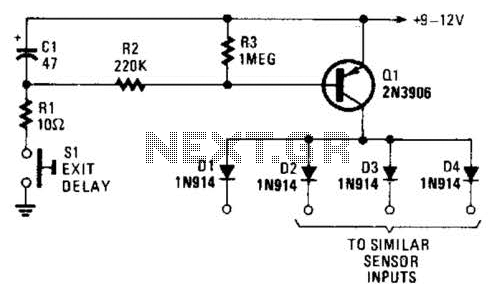

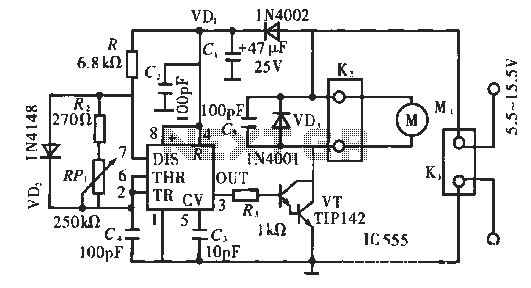

The first design of the LAN tester circuit incorporates the 555 timer IC configured in astable mode to generate a pulse signal. This pulse signal is fed into a decade counter, specifically the CD4017, which counts the pulses and activates the corresponding output pins sequentially. The outputs can be connected to LEDs or other indicators to display the status of the LAN connections. The use of the 555 timer allows for adjustable timing intervals, providing flexibility in how the tester operates. The decade counter's outputs can be used to indicate various conditions such as link status or signal integrity.

The second design employs the ATtiny2313 microcontroller, which offers a more sophisticated and programmable approach to LAN testing. This microcontroller can be programmed to perform a variety of tests, including checking for continuity, measuring signal quality, and providing detailed diagnostic information through a serial interface or LED indicators. The microcontroller's versatility allows for more complex logic and the ability to adapt to different testing scenarios, making it suitable for advanced users who require detailed feedback on network performance.

Both designs serve the essential function of testing LAN connections, but they cater to different levels of complexity and user requirements. The choice between the two designs depends on the specific needs of the user, whether a simple and straightforward testing method is required or a more advanced, programmable solution is preferred.LAN tester circuit diagram provided in two designs. The first design use timer IC 555 and decade counter 4017. The second design use microcontroller ATtiny2313 🔗 External reference

The first design of the LAN tester circuit incorporates the 555 timer IC configured in astable mode to generate a pulse signal. This pulse signal is fed into a decade counter, specifically the CD4017, which counts the pulses and activates the corresponding output pins sequentially. The outputs can be connected to LEDs or other indicators to display the status of the LAN connections. The use of the 555 timer allows for adjustable timing intervals, providing flexibility in how the tester operates. The decade counter's outputs can be used to indicate various conditions such as link status or signal integrity.

The second design employs the ATtiny2313 microcontroller, which offers a more sophisticated and programmable approach to LAN testing. This microcontroller can be programmed to perform a variety of tests, including checking for continuity, measuring signal quality, and providing detailed diagnostic information through a serial interface or LED indicators. The microcontroller's versatility allows for more complex logic and the ability to adapt to different testing scenarios, making it suitable for advanced users who require detailed feedback on network performance.

Both designs serve the essential function of testing LAN connections, but they cater to different levels of complexity and user requirements. The choice between the two designs depends on the specific needs of the user, whether a simple and straightforward testing method is required or a more advanced, programmable solution is preferred.LAN tester circuit diagram provided in two designs. The first design use timer IC 555 and decade counter 4017. The second design use microcontroller ATtiny2313 🔗 External reference